PDN��Դ��ƽ��ȥ������������

�����꣬��������������ż�����ѩ÷�������ģ�����

(���ϴ�ѧ ���������ѧԺ������ ��ɳ��410083)

ժ Ҫ��

�εIJ�ͬ�ֲ����ȥ����������˼�룬����������ȥ��ԭ���ͼ��㷽�����������������ߵȲ�ͬ��װ������ȥ������迹��Ӱ�졣����Ŀ���迹������10 MHz~1 GHz��Ƶ����Χ��PDN�Ķ˿��迹��ƣ�����Ŀ���迹ֵ����г���ȷ��ȥ����ݵ����ࡢ�ͺź���Ŀ������Ansoft SIwave���߶�����Ƶ�ȥ���������ȥ��Ч�����з���ģ�⡣��������������Դ��ƽ���ڸ�Ƶ����Ҫ�ĵ����迹��С����Ƶ�εĵ����迹�ȵ�Ƶ�ε����迹��һ��������������Ҫ��ȥ�������Ŀ����ϰٸ���

�ؼ��ʣ�

��Դ����������Ŀ���迹����Z������ȥ�������

��ͼ����ţ�TN98 ���ױ�־�룺A ���±�ţ�1672-7207(2013)10-4088-06

Decoupling capacitor networks design on PDN power ground planes

LIU Lijuan, YANG Bingchu, NI Lan, ZHANG Jianyang, XU Xuemei, DENG Lianwen, CAO Can

(Department of Physics and Electronics, Central South University, Changsha, 410083, China)

Abstract: To design the decoupling capacitors network according to the hierarchical division, the decoupling principle and computing method were proposed. Meanwhile, the effects of different packings such as vias and traces on the impedance of decoupling capacitors were analyzed. The port impedance of PDN in the frequency range from 10 MHz to 1 GHz was designed with the target impedance method, and the type, model and number of the decoupling capacitors were chosen according to the method and self-resonant frequency of each capacitor. The processing and decoupling effects of the designed decoupling capacitors network were simulated in Ansoft SIwave. The simulation results show that the impendance of capacitor needed among Power and plane structure was small. In high frequency, the impedance of capacitor was reduced an order of magnitude compared with the low frequency, but the quantity raised to hundreds or even more.

Key words: power distribution network; target impendence method; Z parameters; decoupling capacitors

������Ϣ�����ķ�չ�����ָ����ܡ����ܶȡ������������ɵ�·Ӧ�˶�����ϵͳ����Ƶ�ʲ�����������Դ��������ʹ��PDN������ٸ������ս��Ϊʹϵͳ�ܹ���ʱ��Ч��Ϊ���ɵ�·�ṩ���������㡢�ȶ��ĵ�Դ��Ӧ�ôӸ����Ͽ���ϵͳ��һ��Ƶ����Χ�ڹ���ʱ�����迹����Ŀ���迹[1]����������Ч��;����������Ӧ�ļ��ɵ�·(IC)�Է���ȥ����ݡ�����ȥ�������е��������ͺš���С����Ŀ��ѡȡ��ȷ��Ҳһֱ���о����ȵ㡣����PDN��Ƶĸ��ӶȺ;�ϸ�� ����ߣ����ù����ṹ���ۺ��˲���[2]������������뵼�����(MOSCAP)[3]��Ƕ��ʽ����[4]����Ŵ�϶�ṹ(EBG�ṹ)[5-7]�����ʵ�ָ���Ƶ��ȥ����ƣ��Ŵ��㷨[8]�����ֻ��ַ�[9]���ɱ�����[10]����Ч���ݷ����㷨[11]��Ӧ�õ��Ż�ȥ�����������С�Ȼ�������е��о��ɹ�������ֱ��Ӧ���ڸ��ٸ߹���PDN����ƣ������������ھ���ḻ�Ĺ���ʦ����ʱ���ò����з���������ơ�Wang��[12]��ʱ���Ƶ��2��������ڿ���PDN�迹��ȥ���������EBG�ṹ��ȥ��Ч�����з�������û�з���ȥ����ݲ�����ȥ�����õ�Ӱ���Լ�������ȥ��������硣Fizesan��[13]ͨ���ɱ������ķ�������PDNȥ�������Ƶ�ͬʱ���з��������Ȼ��û�п��DZ������ݷ�װ�Թ��������ߵ�ȥ��Ч����Ӱ�졣ȥ����ݵĹ��������ߵȲ������ṹ����ȥ����������������ش��Ӱ��[14]���������߷���������ȥ���ԭ����������ͬ��װ�Ϲ��������ߵȶ�ȥ������迹�ļ�����еļ��㡣Ȼ������Ŀ���迹���о�ȥ����ݵ��ͺź���Ŀѡ�����ơ��������Ansoft��˾��SIwave���߽��з���ģ�⣬��֤������۵ĺ����Ժ���ȷ�ԡ�

1 ȥ���������ԭ�����������

1.1 ��������ȥ��ԭ������

��оƬ����˲̬�仯����ʱ��ȥ�����Ϊ���ɵ�·�ṩ�˾ͽ��ĸ�ǿͨ��������ͨ����Դ�ߴӽ�Զ�ĵ�Դ�л�ȡ�������Ӷ����Ƶ�Դ�����ķ�ֵ[15]��ͬʱҲ����С������ķ���������ʹͨ��֮���֮��û�й����迹�������˹��迹��ϡ�

ͼ1 ��DC~GHzƵ����ΧĿ���迹

Fig. 1 Target impedance in frequency range from DC to GHz

�����PDN�ṹ������ѹ����ȥ��������硢��Դ��ƽ���Լ����ֻ����ṹ��ͼ1���÷ֲ���Ƶ�˼�룬�ڲ�ͬƵ���£���Ҫѡ��ͬ���͵ĵ���������PDNȥ����ơ���1 kHz��1 MHz��Χ�ڣ�����Ƶ����ͨ��������ȥ�����������Ƶ����ѡȡƷ������ԶС��1����������ܹ�ʵ��ȥ���Чѹ��PDN���迹����[16]�����ڸ��ߵ���ֵ�ĵ������ɲ����㡢����ݻ������������10 MHz��100 MHz����Ƶ���ڣ�ȥ����ò�ͬ���ʡ���ͬ�ߴ���մɵ�������

�ڸ�Ƶȥ��ʱ������ȥ���Ƶ�ʷ�Χ�ֳɼ��Σ�ÿһ�ε������㣬�ö����ͬ��ֵ���ݲ����ﵽ�迹Ҫ����Ӧ��ͬƵ�η�Χ��Ӧѡ��ͬ�ĵ��ݡ���������Ƶʱ��Ҫ����Ϊ���ԣ�һ����þ��е͵�е��մɵ��ݡ�

1.2 ������еļ���

��ʵ���У��������������ǵ���(C)����������(RES)�ͼ������(LES)�Ĵ���г���·��RES�ǵ���������ƽ��Ĵ������裬LES���������պͷ�װ�ߴ��йء�ͬ�ַ�װ�ͳߴ�ĵ��ݣ����Ч������л�����ͬ������г��Ƶ���£����������迹��С����RES���������ڵ�����г��Ƶ��ʱΪ���ԣ�������г��Ƶ��ʱΪ���ԡ����迹ģֵ�빤��Ƶ�ʵĹ�ϵʽΪ

(1)

(1)

ͼ2��ʾΪ����Ϊ22 ��F(375 pH��10 m��)��Ƶ����Ӧ��

ͼ2 22 ��F��������Ƶ����Ӧ

Fig. 2 Frequency response of 22 ��F capacitor

�����ڵ�·���ϵİ�װͨ������һС�δӺ��������������ߣ��Լ�2�������Ĺ��ף���������������ڼ�����С������������Ҫ���������Ե��ݵ�����Ӱ������ݰ�װ���Զ�����ΧһСƬ������Чȥ����ȣ������������ڼ�����У��ӵ��ݵ�����Ҫȥ�������·���ϰ������̡�һС�������ߡ����ס���Դ����ƽ�棬�⼸���ֶ����ڼ�����С���Ƚ϶��ԣ����������ߵļ�����нϴ��ļ������Ϊ

(2)

(2)

���У�h0Ϊ���ĺ�ȣ�dΪ���Ŀ��������ߵļ������Ϊ

(3)

(3)

Z0Ϊ�����������迹������Ϊ[17]

(4)

(4)

���У���rΪ��糣����hΪ�ź�����ƽ����ʺ�ȣ�wΪ�߿���tΪ������ȡ��ۺϿ��ǰ�װ���������ߵ����أ�ȥ��������ܵļ������Ӧ����Ϊ

(5)

(5)

2 ȥ������������

PDN���Ҫ������Ҫȥ���Ƶ����Χ���ܹ�����Ŀ���迹���Ա�����ȶ��ĵ�ѹ����IC�˷���ȥ����������ڵ�Դ�͵�ƽ��֮��������PDN���迹������ϵͳ�������PDN��Ŀ���迹�������ʽΪ

(6)

(6)

��Դ��ƽ����Ե�ЧΪ�ɺܶ��к͵��ݹ��ɵ����磬Ҳ���Կ���1������ǻ����һ��Ƶ���£���Щ���ݺ͵�лᷢ��г�����Ӷ�Ӱ���Դ����迹���������10 MHz~1 GHz��Χ��Ϊ����Ȥ�Ĺ���Ƶ�����ڵ�Ƶ�η�Χ�ڣ������������(bulk capacitor)�������迹��ֵ������λ��Ӧѡ��Զ���Դ������ʱ�ӵ�·������������Ӵ��������ڵ�Ƶ�β��ü�������������Ժ�����ʵ�ֿ����迹��Ŀ�ġ�PDN����Ŀ���迹���ٽ�Ƶ�ʵ�ΪFpsw����ߵ�ȥ����ЧƵ��ΪFbypass=Ztarget/(2��L)������LΪȥ��������ĵ�Ч��С���Fpsw��f��FbypassƵ�η�Χ�������ӵ�ȥ�����������ֵ����Ϊ

(7)

(7)

��ѡ���Ƶȥ�������ʱ���ɵ�����Ϊ���ص�·�ṩ˲̬����������һ��ԭ��Ϊ����������г��Ƶ�ʴ��������Ƶ�ʱ��г��Ƶ�ʣ�������ĸ�Ƶ���ݼ�����������㣺

(8)

(8)

ȷ������������Ŀ�ķ���Ϊ����Ƶ������ü����������ݲ����Լ�С��Ч������С����������ͬ�ĵ���ʱ����г��㱣�ֲ��䣬�����迹����ѹ�ʹӶ�����������Ŀ���迹�Ĺ���Ƶ����Χ����Ҫ������ͬ�����ĵ�������ĿΪ

(9)

(9)

ʽ�У�ZCΪ��Fpsw����ȥ������迹ģ��ZtargetΪϵͳĿ���迹ģ��

3 ����ʵ��

��Ʋ���1��4���Դ��ƽ���ģ���·���������桢�ײ㡢��Դ�͵�ƽ�档���е�Դ��ƽ��Եij�����Ϊ100 mm��100 mm��������0.035 mm��ͭƤ�㣬�ɺ��Ϊ0.1 mm ��FR-4epoxy���ʲ��ϸ���������ʳ���Ϊ4.5����SIwave�Ļ����У�����PDN��Դ��ƽ���ģ�͡���ƽ��Ե�(10��10)��(90��90)�����ö˿�P1��P2������VCC��Ground��֮�䣬ϵͳ���Ҫ������10 MHz~1 GHz��Χ�ڶ�PDN�ṹ����P1��P2��Ĵ����迹�������õ�Z����������ͼ3��ʾ��

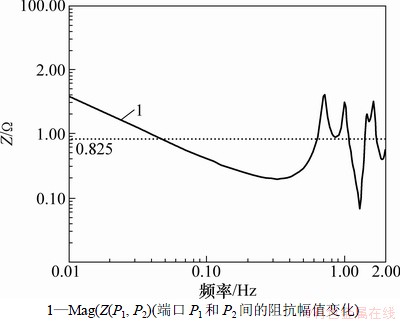

ͼ3 �˿ڴ����迹��Ŀ���迹���߶Ա�ͼ

Fig. 3 Contrast of port impedance and target impedance curve

����ʽ(6)���趨ϵͳ�˿�Ŀ���迹Ϊ��Ztarget= 0.825 ����

Ϊ����Ч���Ƶ�Դ��֮����迹��ͨ������ȥ����������Ͷ˿��迹�����ȶ�ϵͳ����Z�������棬��ͼ3�����ߴ���P1��P2�˿ڴ����迹���ߣ�ֱ�ߴ���Ŀ���迹�������߸���ֱ�ߵ�Ƶ�������ڣ���Դ��ƽ��Ե��迹����Ŀ���迹��������ϴ�Ļ�·��У�ʹ��Դ����ϵͳ�������ѹ�����Ʋ����ޣ��Ӷ������Դ���������⡣

ͨ������ȥ����ݲ��ñ������̷�װ�����弶�����Ҫ���Ӻ��̡������ߺ��ȡ����й��������߽��Ե���ȥ������ܴ��Ӱ�죬��ʵ�ʵ�PDNϵͳ�������Ҫ���Կ��ǡ�����ƹ��ײ���ͨ����ʽ�������������˿ڷֱ����ӵ���Դ�͵ز㣬���ÿ�Ϊ0.5 mm������ΪPDN�弶���0.44 mm�������ߵij����ֱ�Ϊ1 mm��0.5 mm������ʽ(2)��(3)���ֱ�õ����ļ������ΪLm=5.048 nH�������ߵļ������Ϊ0.65 nH/mm�����յõ�ÿ�����ݳ������ļ�����л�����ϰ�װ��У���ֵΪ11.4 nH��

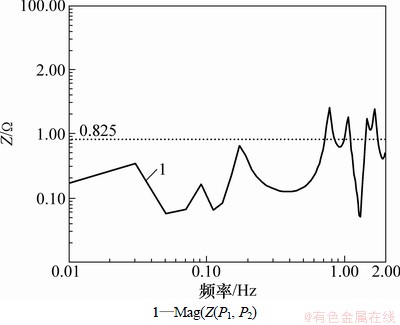

ͨ������������ڵ�Ƶ���ڣ�PDN�˿��迹ֵ�ϸߣ����Բ���1������������ȥ�����ʵ�ֵ�Ƶȥ�����12 ��F������ݵõ��˿��迹��Z����������ͼ4��ʾ��

ͼ4 ���ӵ�Ƶȥ��C1��Z����

Fig. 4 Z curve with low frequency decoupling capacitor C1

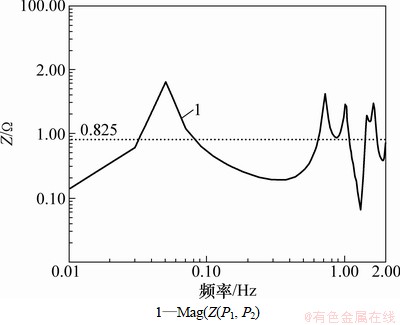

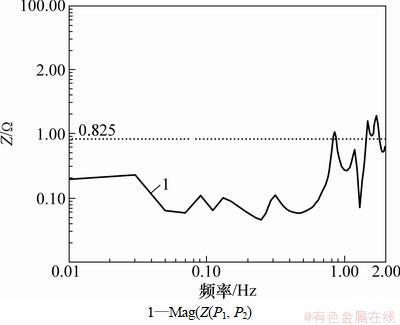

��ͼ4���Կ���������12 ��F����ȥ����ݷ����ڶ˿�P1���������Խ�10 MHz~ 30.1 MHz��Χ�ڵĶ˿��迹����Ŀ���迹���£�ȥ��Ч�����ԡ����ǣ���50 MHz��������1���µ��迹��ֵ���ﵽ6.5 �����ң�ԶԶ����Ŀ���迹�����ϵͳ��������һƵ���£��������ϴ�ĵ�ѹ����������Դ���������⡣�ӽ����������һ��ȥ��ĵ�Ƶ��ΪFpsw=30.1 MHz������ȥ�����ԭ��ʽ(8)�����ӵ������ĵ��ݷֱ�Ϊ��C2=6 nF��C3=2.1 nF��������Ŀ�ֱ�ΪN2=0.798��1��N3=2.17��2����SIwave���ݿ���ѡȡ1206��װ����ֵ�ֱ�Ϊ6.2nF��2.7nF�ĵ��ݡ�ͼ5��ʾΪ������C2�Ķ˿�����迹��Z��������ͼ��

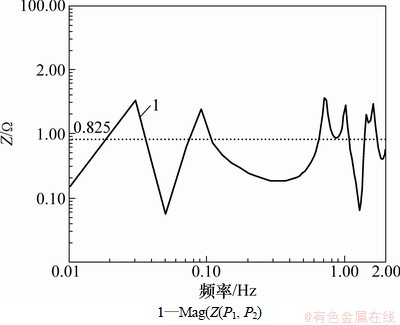

��ͼ5��Z�������߿���������C2֮��Ƶ��30 MHz~60 MHz�迹���ͣ����ҳ���1���迹���ֵ������20 MHz��90 MHz�������迹��ֵ����Ŀ���迹��û����ȫʵ���ڵ�Ƶ�η�Χ�ڵ��迹���ơ�����ͬ��������һ��ȥ��Ϳ��ԴﵽĿ�ġ�ͼ6��ʾΪ����C3����迹���ߡ�

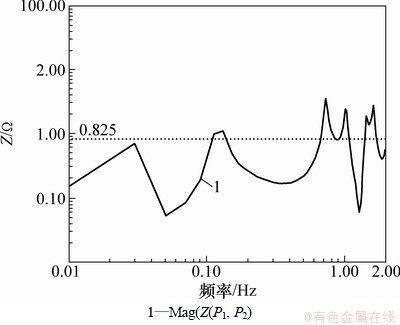

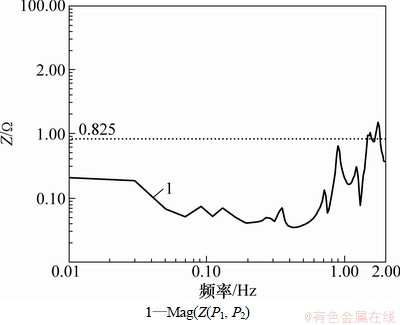

����ͼ6���迹��ֵ����Ŀ���迹���¡����110MHzг���õ��������C4=1.485 nF��1.5 nF��ѡȡ0402��װ��1.5 nF���ݡ������ڵ���������ѡȡʱ������߲����Զ����������RES����ˣ������������һ�������������ԡ�ȥ���������RES���������ƽ̹���迹���ߣ�������߿���ѡ��ͬ��ֵ�ĵ����������ﵽƽ���迹���ߵ����á���ͼ7��ʾ�ķ�������ʾ��������C1~C4��ʵ������10 MHz~700 MHzƵ��������Ŀ���迹�������迹���߽�����õ���Ƶ��ȥ����ݵĵ�1����Ƶ��Fpsw=773.8 MHz����Ƶ��Ҫ�ĵ��������ݺ�С��������Ŀ��϶ࡣ

ͼ5 ����ȥ�����C1��C2��Z��������

Fig. 5 Z curve with decoupling capacitor C1 and C2

ͼ6 ����ȥ�����C1~C3��Z��������

Fig. 6 Z curve with decoupling capacitor C1~C3

ͬ���������ԭ���õ�700 MHz~1 GHz��Ƶ���ڣ����ӵ�ȥ����ݺ���Ŀ�ֱ�ΪC5=0.26 nF��N5=30��C6=0.19 nF��N6=46��ͼ8��ʾΪ��������C5�õ����迹���ߡ�

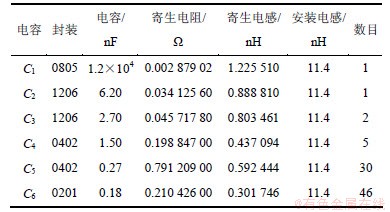

ͼ9��ʾΪ����C6���������ƽ��������Ϊʵ��ȥ��õ��Ľ�Ϊƽ̹�Ķ˿��迹���ߣ���Ȼ�ڹ���Ƶ�η�Χ(10 MHz~1 GHz)�˿��迹������Ŀ���迹���ڡ�������Ʋ�����6�ֲ�ͬ���ࡢ�ͺź���Ŀ�ĵ�����������ȥ���������������PDN��Դ�͵ز�֮�䡣���ͬʱ���Dz�ͬ���ͺͷ�װ�ĵ���������г��Ƶ����ȷ��ȥ�������е����������ࡢ�ͺź���Ŀ��ʵ�� PDN��Դ��ƽ���迹��ơ����⣬ȥ����ݷ���������˿ڸ������Ը���ȥ����ݹ�����ʱ���ԡ���1��ʾΪ���ѡȡ�ĵ�����������

ͼ7 ����ȥ�����C1~C4��Z��������

Fig. 7 Z curve with decoupling capacitor C1~C4

ͼ8 ����ȥ�����C1~C5��Z��������

Fig. 8 Z curve with decoupling capacitor C1~C5

ͼ9 ��ƺ�˿��迹Z��������

Fig. 9 Z curve with decoupling capacitor C1~C6

��1 ȥ����ݲ�����

Table 1 Decoupling capacitor parameter

4 ����

(1) ������ڲ�ͬ�Ĺ���Ƶ���·ֲ���Ƶ�˼�룬�о���������ȥ������������Ʒ�����������ѡȡȥ������ͺš�ȷ�����С����Ŀ���������ݡ���������ص������˱�����װԪ���еĹ��ס������ߵļ�����ж�ȥ��Ч����Ӱ�졣

(2) �ڸ�Ƶ��0.8 GHz~2.0 GHz����Ҫ�ĵ�������ֵ�ȵ�Ƶ�ε�1�����������ֱ�Ϊ0.27 nF��0.18 nF��ͬʱ����Ҫ���ݵ�������������ӣ�0.27 nF��������ĿΪ30����0.18 nF������Ŀ�ﵽ46����

�ο����ף�

[1] ZHANG Mushui, LI Yushan, LI Liping. An efficient power-delivery method for the design of the power distribution networks for high-speed digital systems[J]. IEEE Transactions on Microwave Theory and Techniques, 2009, 57(3): 693-707.

[2] Wu T L, Chuang H S, Wang T K. Overview of power integrity solutions on package and PCB: Decoupling and EBG isolation[J]. IEEE Transactions on Electromagnetic Compatibility, 2010, 52(2): 346-356.

[3] Bharath K, Engin E, Swaminathan M. Automatic package and board decoupling capacitor placement using genetic algorithms and M-FDM[C]//Proceedings 45th Des Autom Conf. Anaheim, CA, 2008: 560-565.

[4] Kikuchi K, Takemura K, Ueda C. Low-impedance power distribution network of decoupling capacitor embedded interposers for 3-D integrated LSI system[C]//IEEE 18th Conference on Electronical Performance of Electronic Packaging and Systems, 2009: 25-28.

[5] Shahpamia S, Ramahi Omar M. Electromagnetic interference (EMI) reduction from printed circuit boards(PCB) using electromagnetic bandgap structures[J]. IEEE Transactions on Electromagnetic Compatibility, 2004, 46(4): 580-586.

[6] Kamgaing T, Ramahi Omar M. Design and modeling of high-impedance electromagnetic surface for switching noise suppression in power planes[J]. IEEE Transactions on Electromagnetic Compatibility, 2005, 47(3): 479-489.

[7] Wang T K, Hsieh C Y, Chuang H H. Design and modeling of a stopband-enhanced EBG structure using ground surface perturbation lattice for power/ground noise suppression[J]. IEEE Transactions on Microwave Theory and Technigues, 2009, 57(8): 2047-2054.

[8] Choi J Y, Madhavan S. Decoupling capacitor placement in power delivery networks using MFEM[J]. IEEE Transactions on Components and Manufacturing Technology, 2011, 1(10): 1651-1661.

[9] Eguia T J A, Mi Ning, Sheldon X, Tan D. Statistical decoupling capacitance allocation by efficient numerical quadrature method[J]. Symposium on Quality Electronic Design, 2009: 309-316.

[10] ZHAO Shiyou, Roy K, Koh C K. Power supply noise aware floorplanning and decoupling capacitance placement[C]// Proceedings of the 15th International Conference on VLSI Design, 2002: 489-495.

[11] WANG Xiaoyi, CAI Yici, ZHOU Qiang, et al. Decoupling acpacitance efficient placement for reducing transient power supply noise[C]//IEEE International Conference on Computer-Aided Design Digest of Technical Papers. 2009: 745-751.

[12] WANG Lixin, ZHANG Yuxia, ZHANG Gang. Power integrity analysis for high-speed PCB[J]. Pervasive Computing Signal Proceeding and Applications, 2010: 414-418.

[13] Fizesan R, Pitica D. Simulation for power integrity to design a PCB for an optimum cost[J]. Design and Technology in Electronic Packaging, 2010: 141-146.

[14] GUO Wei-da, Shiue Guanghwa, LIN Chienmin, et al. An integrated signal and power integrity analysis for signal traces through the parallel planes using hybrid finite-element and finite-difference time-domain techniques[J]. IEEE Tranctions on Advanced Packaging, 2007, 30(3): 558-565.

[15] Song K J, Kim J M, Yoo J W. Low power noise multilayer PCB with discrete decoupling capacitors inside[J]. Circuit World, 2009, 35(2): 30-36.

[16] Archambeault B, Connor S. The effect of decoupling capacitor distance on printed circuit boards using both frequency and time domain analysis[J]. Electromagnetic Compatibility, 2005(2): 650-654.

[17] ����ɽ, ����ƽ. �ź������Է���[M]. ����: ���ӹ�ҵ������, 2005: 149-154.

LI Yushan, LI Liping. Signal integrity: Simplified[M]. Beijing: Publishing House of Electronics Indestry, 2005: 149-154.

(�༭ ���˱�)

�ո����ڣ�2012-08-08�������ڣ�2012-11-12

������Ŀ��������Ȼ��ѧ����������Ŀ(611720747)

ͨ�����ߣ������(1957-)���У�����ʯ���ˣ����ڣ����¹������������о����绰��0731-88879525��E-mail��bingchuyang@csu.edu.cn

ժҪ��������ݹ���Ƶ�εIJ�ͬ�ֲ����ȥ����������˼�룬����������ȥ��ԭ���ͼ��㷽�����������������ߵȲ�ͬ��װ������ȥ������迹��Ӱ�졣����Ŀ���迹������10 MHz~1 GHz��Ƶ����Χ��PDN�Ķ˿��迹��ƣ�����Ŀ���迹ֵ����г���ȷ��ȥ����ݵ����ࡢ�ͺź���Ŀ������Ansoft SIwave���߶�����Ƶ�ȥ���������ȥ��Ч�����з���ģ�⡣��������������Դ��ƽ���ڸ�Ƶ����Ҫ�ĵ����迹��С����Ƶ�εĵ����迹�ȵ�Ƶ�ε����迹��һ��������������Ҫ��ȥ�������Ŀ����ϰٸ���