ģʽ�����õ�NAND Flash����ϵͳ�����ʵ��

�츻�£���Ӧ������Ⱥ����

(���ϴ�ѧ ���������ѧԺ������ ��ɳ��410083)

ժ Ҫ��

flash�洢�����һ��ģʽ�����õľ���ϵͳ�ĵ�·�ṹ���ýṹ����Ԥ������λ��������ƾ���λ����������������һ�ָ��ٲ���BCH������ĵ�·��Ʒ�����������һ���������������������BM�����㷨��Ӳ��ʵ�ַ�����ͨ�����ñ����㷨��·�������㷨��·��ͬʱ�����ˮ������ƹ�Ҳ���������ʵ���Խ�С��Ӳ����Դ������߾���ϵͳ���ܡ��þ���ϵͳ��·��EP4CE15E22C8ϵ��FPGAоƬ��ʵ�֣������в��Է��������Խ������������ͬ��ϵͳ����Ƶ���£��þ���ϵͳ��·�������������Ǵ�ͳ���о�����·��8������Ӳ����Դ����ֻ����1�����봫ͳ��NAND flash������·��ȣ��þ�����·�ṹ��Զ���������ֲ��ǿ�����������Ӧ�ó��ϵ���Ҫ��

�ؼ��ʣ�

Nand flash�洢����������·��������ģʽ��BCH�����ֳ��ɱ����������

��ͼ����ţ�TP919.3 ���ױ�־�룺A ���±�ţ�1672-7207(2013)05-1918-08

Design and implementation of mode reconfigurable NAND flash error correcting system

XU Fuxin, LIU Ying, LIU Yanqun, XIANG Chao

(School of Physics and Electronics, Central South University, Changsha 410083, China)

Abstract: Mode reconfigurable error correcting circuit was presented for NAND flash memory. This circuit can effectively avoid larger error bits than the designed error correcting bits. Hereinafter, a circuit design method of parallel BCH code was brought up, and a kind of BM iterative algorithm hardware implementation was deduced without finite field inverse operation. Based on the multiplexing technology of the codec algorithm circuit and combing pipeline technology with ping-pong operation technology, the performance of the correcting system is improved ingeniously while the increase of the cost is acceptable. The error correcting system circuit is implemented and tested in the FPGA chip of the EP3CE15E22C8 series. Under the same system operating frequency, eight times greater data throughput rate are achieved than those of the traditional serial circuits with only double hardware cost. In comparison with traditional NAND flash error correcting circuit, the present error correcting circuit is relatively independent and portable, and can meet the requirement of several applications.

Key words: NAND flash memory; error correction circuit; reconfigurable mode; BCH code; FPGA

NAND flash�洢�����������ϴ�д�ٶȿ졢��������ʹ�÷�����ŵ㣬�����ڴ������ݵĴ洢����ҵ��õ��㷺Ӧ�á�������NAND flash �洢�ܶȴ�ÿ���洢��Ԫ֮��ľ����С���洢��Ԫ����©������ɱ���[1-2]���п��ܵ���д��洢��Ԫ������������������ݲ�һ�£������ײ������飬��ˣ��ڶ�NAND flash�������ݴ洢ʱ���������ǰ�������������������ݴ洢���ȶ���[3]������NAND flash�㷺ʹ�ã���NAND flash�ľ������Ҳ��Ϊ��ǰ���о��ȵ㡣����������ͨ����Ӧ�ý϶࣬�������ݴ洢�����е�Ӧ���о������ࡣ��NAND flash�Ĵ��������뺺�������Ĺ�ϵ[4]�Ƶ����ľ�����·ʵ�ּ���ֻ�ܹ�����1λ���������-��������(reed-solomon code)��Ƶľ�����·[5-6]����ʵ�ֶԷǶ�����������������·������Ӳ����Դ������Bose-Chaudhuri-Hocquenghen (BCH)�������·�ɾ�����λ����������ٶȿ죬��·������õ��㷺�о�[7-8]��BCH�������·���ѵ��������·����ơ�ŷ��������뷨һ����Բ�����������ʵ�������·[9-10]����ͬ������Ӳ����Դ�������ȱ�㡣�����Berlekamp-Massey(BM)���뷨��Ӧ������BCH���뷨�����������������Ҫ���е����������������������㣬��·ʵ�ֱȽϸ���[11-12]�������뷨Ҳ��һ��Ӧ�ñȽ϶�����뷨[13]����·��������ʱ�䳤�������������ϵͳ��Ҫ��Ϊ�ˣ��������ߴ�NAND flashӦ�õ����忼�ǣ����һ������ʵ�ֵĵ��Ӷȡ�ģʽ�����õľ���ϵͳ��·���������ˮ������ƹ�Ҳ�������������ʽ������������߾���ϵͳ���ۺ����ܡ�

1 ϵͳ����ṹ���

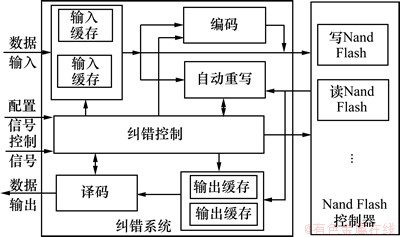

����������о�������������NAND flash��������ͬ�����Ľ��������ܵ�����ƣ�����ϵͳ��NAND flash������������ˮ��ʽ�Ĺ�����ʽ������������������빦��ģ��Ŀ���ֲ�ԡ�������NAND flash��д�����ص����У�����ĵ�1����ˮ����NAND flash�Ķ������ص����У���2����ˮ���������������ͬʱ���У�ͨ��������ˮ�ߵļ��������ٱ����������дNAND flashʱ������ӡ�NAND flash����ϵͳ�ɾ�������ģ�顢������ģ�顢�Զ���д�ж�ģ���Լ���дƹ�һ���ģ����ɡ�����ϵͳ������ṹ��ͼ1��ʾ��

��������ϵͳ��·������Ϊ�ϲ�����ź���ԭʼ���ݣ����Ϊ״̬�ź������������ݡ�������ģ���Ǿ�����Ƶ��ص����ѵ㣬��ģ��ֱ��Ӱ����������������ʡ�

���ǵ��ڴ������洢Ӧ���У�һ��Ϊ��ͨ��NAND flash���й�����Ϊ�˼��ٱ��������ʱ���ڱ�����ǰ�ֱ������ƹ�һ���ģ�顣NAND flash��ҳΪ��λ���ж�д������ÿһҳ��������Ϊ4 096 bit����������Ϊ8λ������ˣ�ƹ�һ���ģ����2��512�ֽ�RAM��ɣ�ʹ�ñ�����ģ������������������ϵͳ�����ʡ�

ͼ1 ����ϵͳ�ṹ

Fig.1 Structure of error correction system

������·ֻ�ܾ�������λ��С�ڵ��ڱ�������Ƶľ���λ���������Ϊ����߾���ϵͳ���������ܣ�����ͨ���е��Զ��ش�����[14]�����1���Զ���д�ж�ģ�����ж�����д��NAND flash�Ƿ�����Ҫ��

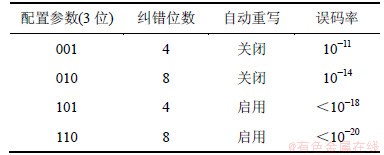

����ģ��ʵ�ֶԾ���ϵͳ�и���ģ�鹤��״̬�Ŀ��Ʋ������Ӧ��״̬�źš�����ģ�������������ò������趨����ϵͳ�Ĺ���ģʽ�������ݿ����ź�������Ӧ��ģ�鹤��������NAND flash�IJ�ͬӦ�ó��ϣ��������ò�ͬ�ľ���ģʽ�����÷�ʽ���1��ʾ��

��1 ����ģʽ����

Table 1 Mode configuration of error correction

2 ����BCH���������

BCH����1�ֿɾ��������������ѭ���룬�����·ʵ�ֱ��������������ˣ�BCH�뱻�㷺Ӧ���ھ���ϵͳ�С���ͳ��BCH�������·���ô��з�ʽ��������Ȼ�ںܶೡ�ϲ�������ϵͳ�����������ʵ�Ҫ��BCH�����·��Լ�ֻ��Ҫ����У��λ���ɡ�BCH�����·�ϸ��ӣ������������3����ɣ���1��Ϊ����У����(si)����2��Ϊȷ������λ�ö���ʽ��(x)����3��Ϊ������λ���������������ڱ�����Ƶ�4�־���ģʽ(����1)������ͬһ�����������㣬��ˣ�������ֻ��У��λ�ij��Ȳ�ͬ����������У��λ�Ĵ����ij���Ϊ���ֵ13�ֽڣ�����ʱͨ�������ź���ѡ����Ӧ���ȣ��������ڸ���ģʽ�¼��ɹ��ñ����·��У���Ӽ����·��������λ������·�Ƕ�ͬ������Ϣλ���в�������ˣ�����ģʽ�¸�ģ����ȫ��ͬ����ͬ�ľ���ģʽȷ������λ�ö���ʽ�ĵ�·�Dz�ͬ�ģ�����Ʒ�����ͬ�������Ծ�4 bit��Ϊ�У����۲���BCH�������·����ơ�

2.1 ����BCH�������

����BCH(n, k, t)�룬��Ҫȷ��3���ؼ����������볤n����Ϣλk��������t��NAND flash��ҳ�ķ�ʽ�洢��ÿҳ������Ϊ4 096 bit����(4 148,4 096,4) BCH��Ϊ�������볤Ϊ4 148 bit����ϢλΪ4 096 bit����������Ϊ4 bit�����DZ�ԭ(8 191,8 139,4) BCH��������룬��xΪ���������������ɶ���ʽg(x)Ϊ

g(x)=x52+x50+x46+x44+x41+x37+x36+x30+x25+x24+x23+x21+x19+x17+x16+x15+x10+x9+x7+x5+x3+x1+1 (1)

BCH����������Ϣλ��У��λ��ɣ���Ϣλ�ڸ�λ��У��λ�ڵ�λ��У��λ��Ϊ��Ϣλ�������ɶ���ʽ����������v(x)��ʾ��Ϣλ����BCH����u(x)������ʽ��ã�

(2)

(2)

ʽ�У� ��ʾ

��ʾ ����

���� �õ���������

�õ��������� ��ʾ4 096 bit����Ϣλ��

��ʾ4 096 bit����Ϣλ�� ��Ϊ52 bit��У��λ��

��Ϊ52 bit��У��λ��

��ͳ�Ĵ��б����·��Ҫ4 096��ʱ�Ӽ��㣬����4 096ʱ�̵������Ĵ�����ֵΪУ���ӡ������ ��ʾ��ǰtʱ�������Ĵ�����ֵ������

��ʾ��ǰtʱ�������Ĵ�����ֵ������ Ϊ8λ���������źţ�����

Ϊ8λ���������źţ����� Ϊ1����

Ϊ1���� �йص�ϵ��������t+1ʱ�������Ĵ�����ֵΪ��

�йص�ϵ��������t+1ʱ�������Ĵ�����ֵΪ��

(3)

(3)

ͨ����ʽ(3)�ĵ���������������8ʱ�� �������Ĵ�����ֵ�뵱ǰ�����Ĵ�����ֵ�Լ�����֮��Ĺ�ϵ���ɵõ��Ĺ�ϵʽ������Ƴ�8λ���еı����·��������·��ͼ2��ʾ��ͼ2�У�b[7:0]Ϊ8λ�����������Ϣλ���ݣ�a[51:0]��c[51:0]�ֱ��ʾǰʱ������һʱ��У��λ�Ĵ�����ֵ�������·����512��ʱ�ӵļ��㼴���Եõ�У��λ���ڼ���У��λ��512��ʱ����ͬʱ������ֵ���Ϣλ�����ڽ�������7��ʱ�����ɸ�λ����λ����������ֵ�У��λ����ɱ��롣

�������Ĵ�����ֵ�뵱ǰ�����Ĵ�����ֵ�Լ�����֮��Ĺ�ϵ���ɵõ��Ĺ�ϵʽ������Ƴ�8λ���еı����·��������·��ͼ2��ʾ��ͼ2�У�b[7:0]Ϊ8λ�����������Ϣλ���ݣ�a[51:0]��c[51:0]�ֱ��ʾǰʱ������һʱ��У��λ�Ĵ�����ֵ�������·����512��ʱ�ӵļ��㼴���Եõ�У��λ���ڼ���У��λ��512��ʱ����ͬʱ������ֵ���Ϣλ�����ڽ�������7��ʱ�����ɸ�λ����λ����������ֵ�У��λ����ɱ��롣

2.2 ����BCH�������

BCH�������������3����ɣ�����У����(si)��ȷ������λ�ö���ʽ��(x)��������λ������������У���Ӽ����·����Ʒ���������·��Ʒ������ƣ������ص����ۺ�2����·��ʵ�֡�

2.2.1 ����λ�ö���ʽ�Ƶ���·

ÿһ��������λ�ö���ʽ�ķ�����Ϊ1�������㷨�����ڶ�������㷨�У���Berlekamp��Massey�����BM���������㷨ʹ����ࡣBM�����㷨��Ч�ʸ��Ҿ������Ӳ��ʵ�ֽṹ���õ��㷺Ӧ�á�BM�㷨�Ǹ���У������ȷ������λ�ö���ʽ ��ϵ��(���У�uΪ����������

��ϵ��(���У�uΪ���������� ��

�� �ֱ�Ϊ

�ֱ�Ϊ �Ĵ�����ϵ��)����

�Ĵ�����ϵ��)���� Ϊ��ǰֵ����һ������ֵ֮�BM�㷨�ĵ�������Ϊ�����ʼֵ

Ϊ��ǰֵ����һ������ֵ֮�BM�㷨�ĵ�������Ϊ�����ʼֵ ��

�� ��

�� ��

�� ����

���� ����

���� ���ı䣬Ϊ

���ı䣬Ϊ ������

������ (����

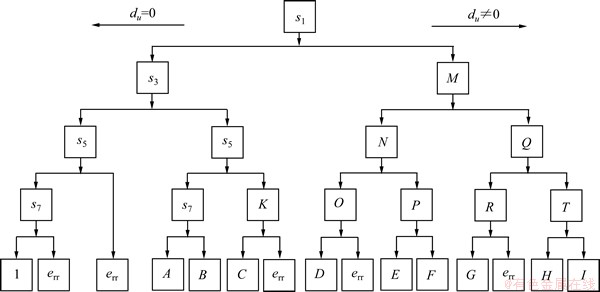

(���У� Ϊ��u��֮ǰ��ֵ��Ϊ0�ĵ�������)����Ȼ��Ҫֱ����Ӳ����ʵ�������������㣬��·�ܸ��ӡ�����BM�������ص㣬��Ծ���λ����С��������Ƶ���һ�ֻ���BM�㷨��������Ӳ���ϵ��������ֱ�����о���[15]������λ�ö���ʽ����4 bit����ֱ�����о���ʾ��ͼ��ͼ3��ʾ��

Ϊ��u��֮ǰ��ֵ��Ϊ0�ĵ�������)����Ȼ��Ҫֱ����Ӳ����ʵ�������������㣬��·�ܸ��ӡ�����BM�������ص㣬��Ծ���λ����С��������Ƶ���һ�ֻ���BM�㷨��������Ӳ���ϵ��������ֱ�����о���[15]������λ�ö���ʽ����4 bit����ֱ�����о���ʾ��ͼ��ͼ3��ʾ��

ͼ2 ���б����·

Fig.2 Circuit of parallel encoder

ͼ3�У������е�ֵ��ʾ��ǰ�����ĵ���ֵ��K��M��N��O��P��Q��R��T��ʾ��ǰ�ڵ�du��ֵ����֪��4 bit����ֱ���о�������ֻ��Ҫ���A��B��C��D��E��F��G��H��I��9������ʽ��err��ʾ����������Χ�Ĵ������������У����ȫΪ��(��)ʱ����������ģ�飬��ˣ�����ߵ�2��·�����Լ���ֻ��Ҫ�ж��ұߵ�13��·������BM��������Ԥ������о�����ÿһ���ڵ�ı���ʽ������Ӳ����ֻ��Ҫִ�����Ӧ��������˷���ӷ����㣬��ˣ��������ӵ�BM������·ת��Ϊ���ݸ����ڵ��ֵѡ�����λ�ö���ʽ����·����״̬���Ƶ�·��

���������ʽHΪ�����Ƶ��������㷨�������� ��

�� ��

�� ��T=0ʱ����BM������������ô�ʱ�Ĵ���λ�ö���ʽΪ

��T=0ʱ����BM������������ô�ʱ�Ĵ���λ�ö���ʽΪ

(4)

(4)

ͬʱ������BM�㷨��ã� ��

�� ������

������ �����ԣ��ڵ�Q���о�����������Ϊ��

�����ԣ��ڵ�Q���о�����������Ϊ�� ��

�� ���Ҷ���ʽ���̳�1����ϵ��������䣬��ˣ����Ի���G�е��������㣬�õ�������Ķ���ʽ��

���Ҷ���ʽ���̳�1����ϵ��������䣬��ˣ����Ի���G�е��������㣬�õ�������Ķ���ʽ��

(5)

(5)

ͨ��ͬ���ķ������Եõ�����·�������������ʽ������ֱ�����о���ֻ��Ҫ3��������˷�����2��������ӷ�����������10��ʱ�������������λ�ö���ʽ����������������̲�����ˮ�߽ṹ����С�˹ؼ�·������ʱ�����ھ�8 bit���������ͬ�����Բ���ֱ�����о�����ֻ��Ҫ����5��������˷�����1��9�����������ӷ����������26��ʱ������ɾ�8 bit��������µ�������λ�ö���ʽ��

2.2.2 ��������������

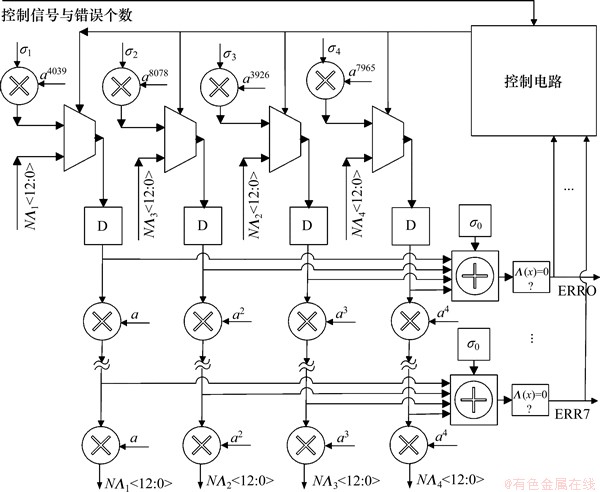

������λ�������ǽ���������ȫ������Ԫ�ش������λ�ö���ʽ��(x)��ȷ�������������λ�����ķ����ж��֣����IJ���Ǯ��(Chien)������·ʵ������λλ�����������Ӧ�ý�����Ӧ�Ż���ơ���ͳ�Ĵ���Ǯ��������·ÿ��ʱ������1��Ԫ�أ���4 bit����Ǯ��������·��Ҫ4��������˷�����1��������ӷ�����Ϊ����������ٶȣ��������1��ʱ�ӿ����������λ�õIJ���Ǯ��������·��

ͼ4��ʾΪ8λ����������·�����ڱ���ʹ�õ�BCH��(4 148,4 096,4)�����DZ�ԭBCH��(8 191,8 139,4)�������룬����Ϣλ�ĸ�4 043λȫΪ0�����������У��λʱ�������4λ0����ˣ���Ϣλ�ĵ�1��Ԫ��Ϊ������ĵ�4 040��Ԫ�أ�������λ���������������Ϊ��4 040��Ԫ�ؼ���1��������Ϣλ���ɽ�ʡԼһ�������ʱ�䡣��Ӳ��ʵ��ʱ�����ó���������Ԫ��a4 039����ȷ���ķǴ���λ�ã��Ա�֤�ɵ�1����Ϣλ��ʼ��������λ�á��ڽ�������512��ʱ���ڽ�ÿһ��Ԫ�ش����(x)���жϱ���ʽ��ֵ������(x)Ϊ0����ǰλ�ü�Ϊ����λ�á�ͼ4�У���1����2����3�ͦ�4Ϊ��(x)ϵ���� ��

�� ��

�� ��

�� ΪǮ�����������е��۳�ֵ������512��ʱ�Ӽ�����ɶ���Ϣλ�������������λ��������ֲ��ģ�ͨ��ͼ4�еĿ��Ƶ�·���������Ĵ���λ�������������������ڴ������ʱ������������ɸ���ͳ�ƿ�֪��������Ƶ�·����ƽ������һ�������ʱ�䣬����������·�Ĺ��ġ�

ΪǮ�����������е��۳�ֵ������512��ʱ�Ӽ�����ɶ���Ϣλ�������������λ��������ֲ��ģ�ͨ��ͼ4�еĿ��Ƶ�·���������Ĵ���λ�������������������ڴ������ʱ������������ɸ���ͳ�ƿ�֪��������Ƶ�·����ƽ������һ�������ʱ�䣬����������·�Ĺ��ġ�

ͼ3 ֱ�����о���

Fig.3 Method of direct tree verdict

ͼ4 ����Ǯ��������·

Fig.4 Circuit of parallel Chien search

��������ĵ�1����Ҫ519��ʱ�����ڣ���2����Ҫ10��ʱ�����ڣ���3����Ҫ512��ʱ�����ڣ���ˣ�����������2����ˮ�ߣ���1����ˮ����У���ӣ���2����ˮ��������λ�ö���ʽ���̲���������λ������

���IJ��ö����������������Ǯ�������ص������ķ����������������ݶ������е���ˮ�������������Ĺ���Ч�ʡ������������ݴ���λ�õ�ͬʱ������ת��Ϊ��Ӧ��������������еĴ洢��ַ�����Ըô洢��ַ�е����ݾ����������������ȷ���ݡ�

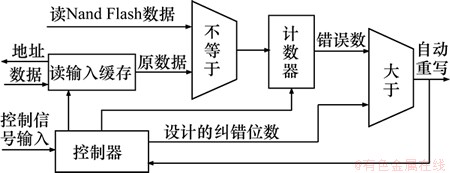

3 �Զ���д�ж�

�������Ĵ���λ��������Ƶľ���λ��ʱ����ͳ�������·���ܹ���������Ϊ�˷�ֹ��������������������1���Զ���д�ж�ģ�飬���ֲ������������ܵIJ��㣬ͬʱҲ�����ڶ�NAND flash�Ļ���������Զ���д�ж�ģ���ɾ���ϵͳ����ģ�鷢���Ŀ����ź��趨����״̬����������Ϊ���û��߹ر�״̬�����·ԭ����ͼ5��ʾ���乤��ԭ���ǽ�����������д��NAND flash��NAND flash������Ϣλ��ԭʼ���ݽ���������㣬���������Ľ���жϷ��������λ���������ִ���λ��������Ƶľ���λ��ʱ������ֹͣ�Ƚϲ������Զ���д�źţ����½�����д�������ҳ������������ĸ���С����Ƶľ���λ��ʱ����һֱ�Ƚ���512���ֽڣ�������д��ɹ��źš��üĵ�·��ʹ�����ʴ�ͣ������ܹ��Ե���NAND flash��������д���������ڶԶ��NAND flash����д����ʱ������ƹ�Ҳ�������������ʵ������д������

ͼ5 �Զ���д�ж�

Fig.5 Judgment of automatically rewrite

4 ��������֤

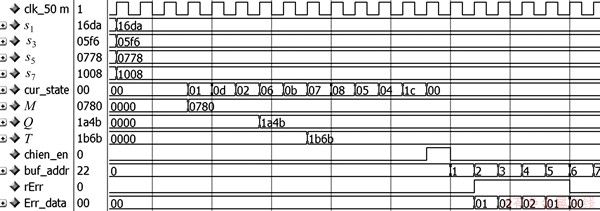

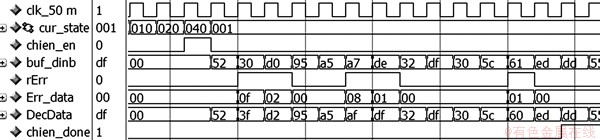

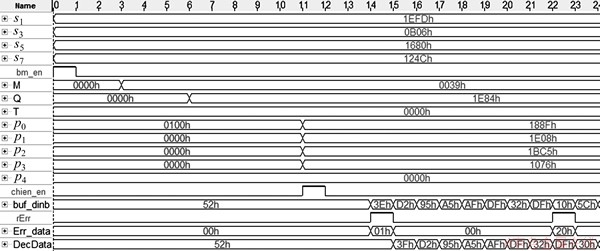

������Ƶľ���ϵͳ��·ʹ��verilog�������RTL����ƣ�ʹ��Quartus������ɵ�·�ۺϣ�ͬʱʹ��ModelSim��SignalTap��������ʱ���������֤��ͼ6~8�У�clk_50mΪ����ϵͳ��·��ϵͳʱ�ӣ�cur_stateΪ���������ʽ��״̬����M��Q��TΪǰ���Ƶ��ĸ��ڵ�du��bm_enΪ����������·ʹ���źţ�chien_enΪǮ������·ʹ���źţ�buf_dinb��buf_addr�ֱ�Ϊ�����������������ݵ�ַ��rErr_addr��Err��Err_data����ֱ�Ϊ�����ַ��������־������У�����ݣ�DecDataΪ����������ݡ�

ͼ6��ʾ������Ϊ��4 bit���ǵ��������ʱ��ͼ����ͼ6��֪�������·���յ�ʹ���ź���ʼ���룬��������4��У����(s1��s3��s5��s7)��ֵ������������У���ӵ���0����ֱ�ӽ������룬����ʹ��������λ�ö���ʽ��·������10��ʱ�Ӽ��������λ�ö���ʽ��ϵ��������ʹ��Ǯ������·(chien_enΪ�ߵ�ƽ)��Ǯ������·ÿ��ʱ��ͬʱ����8��λ�á�����������λ�ú����ݼ����У�����ݣ��Դ������ݾ�����ͼ6��ʾΪ����Ϣλ�ĵ�3������6���ֽ��ϸ�����1bit���������

ͼ7��ʾ�Ǿ���ϵͳ��·����Ϊ��8 bit��ʱ���������ʱ��ͼ�������벽�����4 bit��ʱ��ͬ������8��У����(δ��ͼ�и���)����ֵ�ֱ�Ϊ��s1=0 978h(��h��ʾ16����)��s3=1 864h��s5=0A2Fh��s7= 0FCCh��s9=1175h��s11=15D1h��s13=0B8Ch��s15=0673h������У���Ӳ�����0���ʿ�ʼ�����λλ�ö���ʽ��������8 bit��ʱ����Ҫ26��ʱ�Ӽ������λ�ö���ʽϵ��p0~p8(δ��ͼ�и���)����ֵ�ֱ�Ϊp0=1936h��p1=144Dh��p2=12ECh��p3=DE50h��p4=0595h��p5=0316h��p6=0CA7h��p7=0069h��p8=1F3Ch������8��У��ֵ��9������λ�ö���ʽ��ϵ������ͼ7�е����ݼ�������ġ�ͼ7�У�����Ϣλ�ĵ�2���ֽ���������������ʹ�ܾ�����־�ź�(rErrΪ�ߵ�ƽ)��ͬʱ����У������0Fh������������λ���õ������������3Fh������������12����Ϣλ��������ȫ��8������λ���������������������������ɱ�־�ź�(chien_doneΪ�ߵ�ƽ)��

����ϵͳ��·������Altera��˾��EP4CE15E22C8ϵ��FPGAоƬ��ʵ�֡����ñ��ķ�

��ֻ��Ҫ3 643������Ԫ��Ӳ����Դ������������FPGA��ʵ��ģʽ�����õľ���ϵͳ��·����ƣ�����֤������·������50 MHzʱ�����������ʿɴ�390 Mb/s���Ǵ�ͳ����ģʽ�µ�8����ͼ8��ʾ����SignalTap���߲���������Ϊ��4 bit����ʱ�ľ���ϵͳ��·����ʱ��ͼ��ͼ6�У�����ʱ�̼�����У���ӣ���У���Ӳ�Ϊ0����ʹ��BMģ��(bm_en�ߵ�ƽ)������λ�ö���ʽ��ͼ8�У�����3 bit��������Ҵ������ʽ��·��ΪH��������BMģ���ĵ�3��ʱ���ж�M����M��Ϊ0�����ڵ�6��ʱ���ж�Q����Q��Ϊ0�����ڵ�9��ʱ���ж�T����T��Ϊ0������ô���λ�ö���ʽ��ϵ����ΪH��Ӧ��ֵ���������λ�ö���ʽϵ��p0��p1��p2��p3��p4������ִ��Ǯ���������ݻ����ַ1�ϵ�����2Fh���ڵ�5λ����1 bit�������ݡ�Ǯ�������ĵ�2��ʱ���ѵ�����λ�ò������У������10h��������������У�����ݽ���������㼴�õ��������ȷ����3Fh����������ʱ��ͼ̫��������ֻ��ʾ��������������̡�

ͼ6 ����4 bit���ķ��沨��

Fig.6 Simulation waveform of correction of 4 bit error

ͼ7 ����8 bit���ķ��沨��

Fig.7 Simulation waveform of correction of 8 bits error

ͼ8 FPGA��ʵ�ֵ�����ʱ��ͼ

Fig.8 Decoding timing diagram acquired from FPGA

5 ����

(1) ���һ��ģʽ�����õ�NAND flash����ϵͳ��·�ṹ�����������뼼�����Զ���д�жϼ������ϣ�������NAND flash�������ʡ�

(2) ��ͬ�ȴ洢�����빤��Ƶ���£��þ���ϵͳ��·���и��ߵ����������ʣ���ÿ������NAND flash��д��������ݡ�

(3) ����ͬ�����ݴ���������NAND flash����ϵͳ��·�����ĵ�ʵ�ַ������и���Ӳ���ṹ������С��Ӳ����Դ�Ŀ�����

(4) ����IJ�ͬNAND flash������·��Ʒ����Խ���NADN flash�����������д�ٶ���һ�������塣ͬʱ���þ���ϵͳ��·�ṹ������������ֲ�������ڶ��ֲ�ͬ��NAND flashӦ�ó��ϡ�

�ο����ף�

[1] Kang M G. DIBL-induced program disturb characteristics in 32-nm NAND flash memory array[J]. IEEE Transactions on Electron Devices, 2011, 58(10): 3626-3629.

[2] LI Longzhen, Lee J H, Kim T H, et al. Design of small-area multi-bit antifuse-type 1 kbit OTP memory[J]. Journal of Central South University of Technology, 2009, 16(3): 467-473.

[3] LI Shu, ZHANG Tong. Improving multi-level NAND flash memory storage reliability using concatenated BCH-TCM coding[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2010, 18(10): 1412-1420.

[4] ZHANG Chong, HUANG Mengshu, Okamura L, et al. Error rate decrease through Hamming weight change for nand flash[C]// Proceedings of 2010 10th International Symposium on Communications and Information Technologies. Tokyo, Japan: IEEE, 2010: 1079-1082.

[5] WANG Fangyu, HE Xin, ZHU Wei, et al. Error detection and correction algorithm for RS code based on storage with flash memory[J]. Computer Engineering, 2011, 37(12): 245-247.

[6] Ganesh B, Muralidharan D. Efficient VLSI architecture for low complexity parallel reed solomon decoder[J]. European Journal of Scientific Research, 2012, 73(1): 1079-1082.

[7] LIN Yimin, Yang C H, Hsu C H, et al. A MPCN-based parallel architecture in BCH decoders for NAND flash memory devices[J]. IEEE Transactions on Circuits and Systems ��: Express Briefs, 2011, 58(10): 682-686.

[8] DONG Guiqiang, XIE Ningde, ZHANG Tong. On the use of soft-decision error-correction codes in NAND flash memory[J]. IEEE Transactions on Circuits and Systems ��: Regular Papers, 2011, 58(2): 429-439.

[9] XU Yajie, MA Zhi, ZHANG Chunyuan. On classical BCH codes and quantum BCH codes[J]. Journal of Electronics, 2009, 26(1): 64-70.

[10] Kazuaki D, Hideichi S. Quasi-maximum-likelihood-decoding based on hare decision of BCH-code beyond BCH-bound[J]. Science and Engineering Review of Doshisha University, 2003, 44(3): 177-184.

[11] WU Yingquan. New list decoding algorithms for Reed-Solomon and BCH codes[J]. IEEE Transactions on Information Theory, 2008, 54(8): 3611-3630.

[12] Park J I, Lee H. Area-efficient truncated Berlekamp-Massey architecture for reed-solomon decoder[J]. Electronics Letters, 2011, 47(4): 241-243.

[13] Hu T H, Chang M H, Su I J. A modified step-by-step decoding for binary BCH codes[J]. International Journal of Electrical Engineering, 2006, 13(4): 397-404.

[14] Ф��, ��·��, ��ΰƽ. ��������������л����������Ĺ㲥�ش�����[J]. ���ϴ�ѧѧ��: ��Ȼ��ѧ��, 2008, 39(6): 1291-1295.

XIAOXiao,YANGLuming,WANGWeiping. High loss wireless broadcasting retransmission scheme based on network coding[J]. Journal of Central South University: Science and Technology, 2008, 39(6): 1291-1295.

[15] Bellorado J, Kavcic A. Low-complexity soft-decoding algorithms for reed-solomon codes. Part ��: An algebraic soft-in Hard-O[J]. IEEE Transactions on Information Theory, 2010, 56(3): 945-959.

(�༭ �²ӻ�)

�ո����ڣ�2012-06-07�������ڣ�2012-08-22

������Ŀ��������Ȼ��ѧ����������Ŀ(61178017)

ͨ�����ߣ��츻��(1965-)���У����������ˣ������ڣ����¹����Ϣ�������������������о����绰��0731-88836313��E-mail: xfx.300@163.com

ժҪ�����NAND flash�洢�����һ��ģʽ�����õľ���ϵͳ�ĵ�·�ṹ���ýṹ����Ԥ������λ��������ƾ���λ����������������һ�ָ��ٲ���BCH������ĵ�·��Ʒ�����������һ���������������������BM�����㷨��Ӳ��ʵ�ַ�����ͨ�����ñ����㷨��·�������㷨��·��ͬʱ�����ˮ������ƹ�Ҳ���������ʵ���Խ�С��Ӳ����Դ������߾���ϵͳ���ܡ��þ���ϵͳ��·��EP4CE15E22C8ϵ��FPGAоƬ��ʵ�֣������в��Է��������Խ������������ͬ��ϵͳ����Ƶ���£��þ���ϵͳ��·�������������Ǵ�ͳ���о�����·��8������Ӳ����Դ����ֻ����1�����봫ͳ��NAND flash������·��ȣ��þ�����·�ṹ��Զ���������ֲ��ǿ�����������Ӧ�ó��ϵ���Ҫ��