DOI: 10.11817/j.issn.1672-7207.2015.06.022

GNSS�źŲ����е�α������ղ�������

������������������ά��ŷ��

(�����Ƽ���ѧ ���ӿ�ѧ�빤��ѧԺ������ ��ɳ��410073)

ժ Ҫ��

��ϵͳ(GNSS)�źŲ����д���α������գ����һ�ֻ���ʱ�ӿ��Ƶ�α������ղ���������ͨ�������ӳ��˲�����������α�����������ı�����ͽ����źŵ���λ��ƥ�䡣��������������ղ������ڵ��µ�GNSS�źŲ���ṹ������ȫ��λϵͳ(GPS)C/A���źŽ��з�����֤���о�����������ӳ��˲�������Խ��������յIJ���Ч��Խ�ã��ڲ�����Ϊ5 MHzʱ����������Farrow�ṹ�ķ������ӳ��˲���������Ľ�����0.2 dB��

�ؼ��ʣ�

ȫ������ϵͳ��α������ղ�����ʱ�ӿ������ɱ�������ӳ��˲�����

��ͼ����ţ�TF803.21 ���ױ�־�룺A ���±�ţ�1672-7207(2015)06-2134-08

Code Doppler compensation method for GNSS signal acquisition

HUANG Xinming, GONG Hang, ZHU Xiangwei, OU Gang

(School of Electronic Science and Engineering, National University of Defense Technology, Changsha 410073, China)

Abstract: A code Doppler compensation method based on delay control was proposed to remove the influence of loss in acquisition performance because of code Doppler during global navigation satellite systems (GNSS) signal acquisition. Compensation of code Doppler was achieved by compensating the phase difference between the received and local signals with a digital delay filter. A new GNSS signal acquisition structure, including code Doppler compensation processing, was provided. Performance of the compensation method was analyzed and verified by simulation. The results show that the higher the order of the digital delay filter, the better the compensation performance. Moreover, detection loss can be reduced to less than 0.2dB with a 3th-order fractional delay filter realized by FARROW structure.

Key words: global navigation satellite system (GNSS); code Doppler compensation; delay control; variable fractional delay filter

���Ǻ��û�֮�������˶������ջ�������ϻ��ȶ���ʹ�ý��յ����źź��ж����գ������ز������պ��������[1]����һ������£�������ս�С��ֻ���ز������յļ���������ǧ��֮һ����ˣ��ڳ���Ľ��ջ�����ʱͨ���������źŵ�������մ�����Ӱ��[2-3]�����Ƕ��ڸ������Ƚ��ջ����ò�����������յ�Ӱ�죬�ر��ǵ��û���̬�ϸ�ʱ��������ճ�Ϊ��һ�����ò����ǵ����ء��������Ƚ��ջ���Ҫ�ϳ��Ļ���������㹻������ȣ��������ڴ���������գ�������ͽ����ź�֮���������صIJ�ƥ�䡣�ڼ�������£���α�������Ƶ������ɵ���Ƭ֮��IJ�ƥ�䳬�������Ƭʱ��������ɻ���ʱ�䲻������������棬�����ή�������źŵIJ������ܣ���ˣ���Ҫ��������ս��в�����������ն��źŲ����Ӱ�������ڽ����źźͱ��������źŲ�һ�µ��µ�����ط�ֵ����ϡ����Ҫ����������յ�Ӱ�죬����Ҫ�������ջ������ǵ�������֮��IJ�һ������һ��������ղ�����ֱ�۷�ʽ���Ǹ����ز���α��ı�����ϵ�������ز�����α�룬�ڸı��ز�����������������ͬʱҲʵʱ�ı䱾��α���������ʣ����ز��������������ʱ��α�������Ҳʵ���˲�����Ȼ����������GNSS�źſ��ٲ����й㷺Ӧ�õĻ��ڿ��ٸ���Ҷ�任(FFT)���źŲ���ṹ[2]������������ղ���������ʹ����ʵ���ѶȼӴ���Ϊ�ı䱾�������������Ƶ�ʾ���ζ�ű��������FFT�任�ĵ���һֱ�ڱ䡣ͬ�������ֲ�������Ҳ�������ڻ���ƥ���˲����IJ��в���ṹ[4]��������Ϊ����������Ƶ�ʵij����仯��ʹƥ���˲�����ϵ����Ҫ����ˢ�£��⽫����ʵ�ֽṹ�����Լ�����ʱ�����ӡ���ˣ�ͨ���ı䱾��������Ƶ��ʵ�ֶ����ղ����Բ���ʱ��Ҫ��ܸߵĸ������ȵ����źŲ�����˵�����Ǹ��ܺõĽ���� ��[5]�������������һ�ֻ���ʱ�ӿ��Ƶ�α������ղ���������ͨ��ʵʱ���������ź��ӳ����������յIJ��������Բ���Ҫ�ı䱾���������Ƶ�ʡ�ͨ�������������ǰ��������ն��źŲ����Ӱ�졣ͬʱ��Ҳ�����˸÷�����ʵ�ֽṹ������������Ӧ�ķ��������

1 α������յ�Ӱ�����

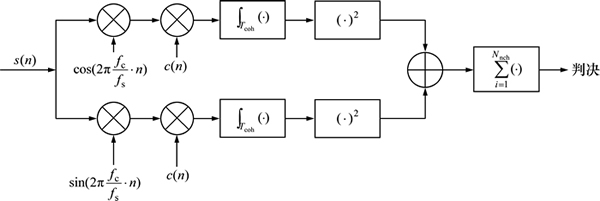

�������ջ�����IJ���ṹ��ͼ1��ʾ[1]������ADC���������Ƶ�źſ��Ա�ʾΪ

(1)

(1)

���У�AΪ�źŵķ��ȣ�D(n)Ϊ�����������ݣ�C(n)Ϊ��Ƶ�룻fIFΪ��ƵƵ�ʣ�fDΪ������Ƶ�ʣ�TsΪϵͳ�������ڣ�w(n)Ϊ������䷽��Ϊ ��

��

�ڲ�������������£�������ػ��ַ���ɺ��������ļ����ֵΪ

(2)

(2)

���У�NncΪ����۴�����fdΪ����������Ƶ�ʣ�TcohΪ��ػ���ʱ������Ϊ����Ƭ����TcΪ��λ������λ�ӳ٣�R(��)Ϊ�������غ�����w(n)Ϊ��������Կ����������������ز��������Լ�α����λ����йء���ػ��ֺ�Ļ���ֵI(n)��Q(n)�е�������������̬�ֲ�[1]����(2)ʽ�����ķ���ɻ��ۺ�ļ����V�������ɶ�Ϊ2Nnc�Ŀ����ֲ���

��������źŲ����龯��ΪPFA������Ӧ�IJ�������ֵ��������ʽȷ����

(3)

(3)

��Ӧ�ļ�����Ϊ

(4)

(4)

���У���Ϊ�����IJ��������ù�һ����ֵ�����ɶȶ��壬Ϊ ��

��

��������˳��浼���źŵIJ���ṹ���䲶�����ܣ��������α������նԲ������ܵ�Ӱ�졣

���ջ����źŲ������һ����ͨ����ij�������źŵ��ز�Ƶ�ʺ�����λ���ά����ɨ��ʽ��������ɵġ�ͨ����û�п���������յ�Ӱ�죬���ڳ���������ǿ��Եģ���Ϊһ�������������ձȽ�С�������ܵĻ���ʱ��϶̣�����������������λ�����Ǻܴ�ʽ(2)�е�ͳ�Ƽ������Ӱ���С��������������źűȽ������ᵼ����Ҫ�ϳ��Ļ���ʱ�䣬��ʱ������յ�Ӱ��Ͳ��ܺ��ԡ�Ϊ��ֱ������������նԲ������ܵ�Ӱ�죬�ο�����[6]��������ͬ����ʱ����α���ֵ��ģ���ֵ��Ķ���Ϊ

(5)

(5)

ͼ1 ���浼���źŵIJ���ṹͼ

Fig. 1 Scheme of conventional GNSS signal acquisition structure

���У�R(��)Ϊ����������������µ���ط�ֵ��R0(��)Ϊ��������������µ���ط�ֵ��

����������������µIJ�������ͬ������(3)��(4)ʽȷ������ͬ�������еķ����IJ���Ϊ

(6)

(6)

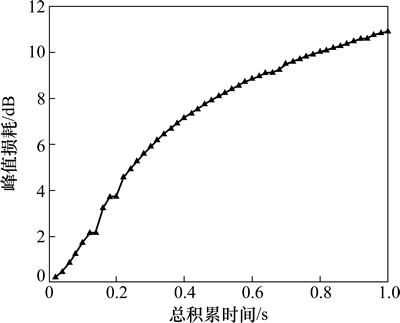

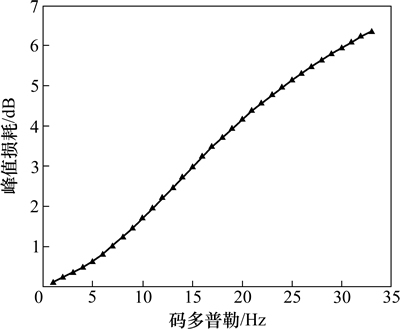

����GPS C/A����з�����֤��������Ϊ1.023 Mcps����������Ϊ5 MHz��������þ����ձ��������ɻ��ּӷ���ɺ���۵ķ�ʽ�IJ���ṹ�������ܵĻ���ʱ����α���ֵ��ĵĹ�ϵ����������ͼ2��ʾ����ʧһ���ԣ�ѡȡ��ػ���ʱ��Ϊ20 ms���������ȡ5 Hz����ͼ2���Կ����������ܻ���ʱ�������α�����������ķ�ֵ���Խ���ԣ����ܻ���ʱ�佫��1 sʱ��α���ֵ��ĸߴ�11 dB����������Ķ��ڵ����źŲ�����˵�������̵ģ���Ҫ��������ս��в�����

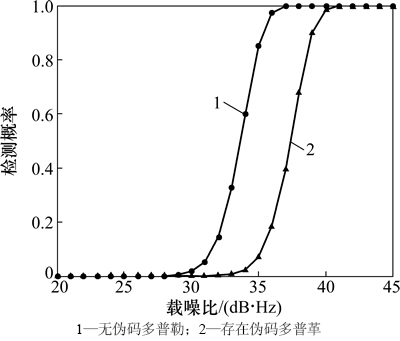

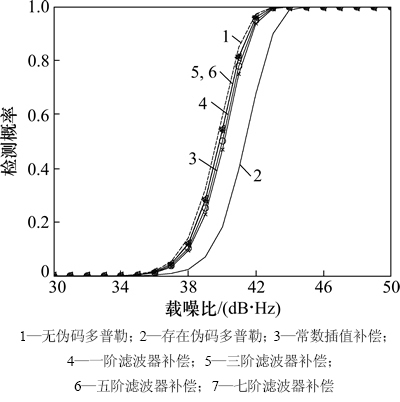

ͼ3�������ܻ���ʱ��Ϊ100 msʱ����α������պ�û��α������յIJ������ܶԱȣ��ɼ�����α�������ʱ������ܳ����˽������½���

ͼ2 ��ͬ����ʱ���µ�α���ֵ���

Fig. 2 Correlation peak loss under different integration time

ͼ3 ��ͬ�����C/N0�����µļ������

Fig. 3 Detection performance under different C/N0

2 ����ʱ�Ӳ�����α������ղ�������

���ݲ��õķ�����ͬ��α������յIJ������Բ�ͬ��������ʱ���õ��dz���ɻ��۵ķ���������Ҫ����ɻ���ǰ���α������յIJ����������õ�����ɻ��ۼӷ���ɺ���۵ķ�ʽ��ǰ�����ɻ���ʱ��϶̣��������Ľ�С��������ڻ��ֺ����α������յIJ������Խ�ʡӲ����Դ��������˵��2�ַ����Ļ���ԭ����ͬ����֮ͬ������α������ղ�����λ�ò�ͬ��Ҳ������2��λ�þ�����α������ղ�������������Ч�����Ӿ�ϸ����Ȼ����Ӳ����Դ����

2.1 ʵ��ԭ��

��GNSS���ջ��У�ͨ��α����������(NCO)���ɵı���α���źſ��Ա�ʾ���£�

(7)

(7)

���У�TcΪ����α���źŵ����ڣ� Ϊ����α���ź��������ڣ�p(t)Ϊ��Ӧ���ǵ���Ƭ���Σ�ckΪ��Ӧ����α�����еĵ�k��Ԫ�ء�

Ϊ����α���ź��������ڣ�p(t)Ϊ��Ӧ���ǵ���Ƭ���Σ�ckΪ��Ӧ����α�����еĵ�k��Ԫ�ء�

Ϊ�˳������������յIJ���������������辭���±�Ƶ���ز������Ľ����ź�û�в�����ز������գ�����Ҳ���й�һ�������Ա�ʾ���£�

(8)

(8)

���У�TsΪ����Ƶ�ʣ�fdΪ�������Ƶ�ʡ�

���ڶ����յ�Ӱ�죬���յ����źŻ�����ź����ڵ�����ѹ�����������źŵ����ڻ�����С��������ʱ��ϳ�ʱ�����������α����λ�ͻ�ٶ��룬�����ͻ�Ӱ���źŵĻ������档�ر��ǵ�����α��ͽ����źŵ�α�뻬���������α������ʱ���������ӻ���ʱ�佫�����ڲ������ܵ������������ή�Ͳ������ܡ�������Ϊα����λ���������Ƭ����۵��źŹ���û�л��۵���������ǿ��Ϊ�˱���������մ����IJ���Ӱ�죬һ��ֱ�۵Ľ��;������ʹ�ý��յ����źŵ�α��ͱ������ɵ�α�������еIJ����㶼���ֶ��룬��C(n)=Cd(n)����ˣ����ջ��IJ������ںͱ���α��������źŵ�������Ҫ������ʽ��

(9)

(9)

Ϊ�˱�֤����α��Ƶ�ʵĺ㶨������ʽ(9)�����ջ��IJ���Ƶ����Ҫ���Ŷ����յĵ�����������������ʽ(9)��Ȼ�������ջ���A/Dת����ͨ��û������ʵʱ�ı��źŵIJ����ʣ��������յ��źŵIJ������Ǻ㶨�ģ���ˣ��ı����Ƶ�ʵķ���Ҳ����ȡ�����������һ��ͨ�������˲�����ɶ����ղ����ķ���������Ҫ�ı����Ƶ�ʡ�����ʽ(8)�������յ��ź�Ҳ���Ա�ʾΪ

(10)

(10)

���У� �����������빦�ܡ���Ȼ�����ڴ���������գ����յ����źźͱ����������������֮�����ʱ�Ӳ�ƥ�䣬����������������ӳ�

�����������빦�ܡ���Ȼ�����ڴ���������գ����յ����źźͱ����������������֮�����ʱ�Ӳ�ƥ�䣬����������������ӳ� �ͷ������ӳ�

�ͷ������ӳ� ���ɼ���ֻҪ�ܹ���ÿ�������㲻ƥ��������������ӳٺ�С���������ӳٲ��������ܹ�ʵ��α��Ķ����ղ�����

���ɼ���ֻҪ�ܹ���ÿ�������㲻ƥ��������������ӳٺ�С���������ӳٲ��������ܹ�ʵ��α��Ķ����ղ�����

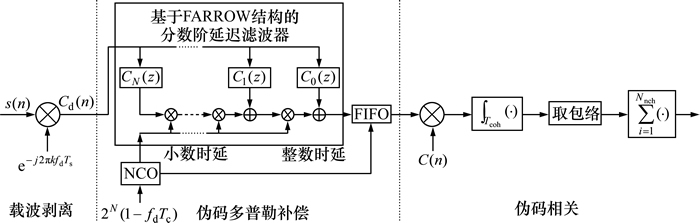

��������ԭ�����������������һ�ֻ�������ʱ�ӿ��Ƶ�������ղ����������������˰���������ղ������ڵ��µ�GNSS�źŲ���ṹ��ͼ4��ʾ���µ�GNSS�źŲ���ṹ����3�����֣���������롢α������ղ�������ɻ��ۡ���������������ɻ��۵Ȳ����ʹ�ͳ�IJ���ṹʵ�ַ�����ͬ��������ղ�����ͨ��ʱ�ӿ���ʵ�֣�����������������ӳٺͷ������ӳ١������������ӳٲ��������ȳ�(FIFO)�ṹ�Ĵ洢������ʵ�֣����������ӳٲ���FARROW�ṹ�ķ������ӳ��˲���ʵ�֡��ɱ�������ӳ��˲��������ʵ�ֿ��Բο�����[7-19]������ķ����������������Ŀɱ�������ӳ��˲�����

����ʱ�ӿ��Ƶ�������ղ���������Ҫʵʱ��ȡʱ�Ӳ���ֵ�����ڲ�����ƥ��������������ӳٺ�С���������ӳ١��������NCO�ķ�ʽ��ȡ�������IJ�ƥ���ӳ٣���ʵ�ֽṹ�볣��NCO��һ�£�����ʵ�ּ�����[1]����������������ָ�ꡣ��ͼ4���Կ�����NCO������ۼӿ�����Ϊ (���У�NΪNCO���ۼ�λ��)���ۼӵ����ֵ���ڿ��������������ӳ٣�δ����ۼ�ֵ���ڿ���С���������ӳ١����У�������յ�ֵ�����ز���α��ı�����ϵ��ȷ�����ӳٲ����ķֱ���Ϊ

(���У�NΪNCO���ۼ�λ��)���ۼӵ����ֵ���ڿ��������������ӳ٣�δ����ۼ�ֵ���ڿ���С���������ӳ١����У�������յ�ֵ�����ز���α��ı�����ϵ��ȷ�����ӳٲ����ķֱ���Ϊ ��

��

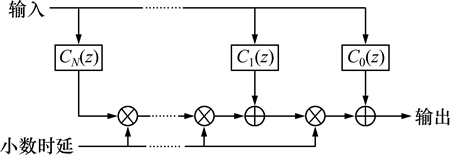

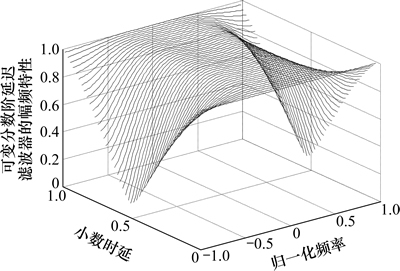

2.2 �ɱ�������ӳ��˲��������

�ɱ�������ӳ��˲�������FARROW�ṹ�ķ������ӳ��˲���ʵ�֡�����[7-19]�����˿ɱ�������ӳ��˲��������ʵ�ַ�����һ�������Ǹ��ݸ����ķ�Ƶ�Լ���Ƶ����ָ������˲���ϵ���Լ���������һ�������Ե��Ż����⣬����ѶȽϴ������Ƚ���FARROW�ṹ�ӳ��˲����Ļ���ʵ�ֽṹ��Ȼ�����һ�ּ��е���Ʒ�����

FARROW�ṹ�Ŀɱ��ӳ��˲�������ԭ���Dz��ö���ʽ����˲���ϵ�������˲���ϵ�����Ա�ʾΪ

(11)

(11)

�˲������亯�����£�

(12)

(12)

���У�NΪ���˲����Ľ�����PΪ����ʽ�������ýṹʾ��ͼ��ͼ5��ʾ����ͼ5���Կ������ýṹֻ��Ҫ����ʱ��ֵ�Ϳ���ʵ�ֿɱ�ʱ�ӵĿ��ơ�

Ϊ�˼�FARROW�ṹ�������ӳ��˲�������ƣ��������һ�ּ��е���Ʒ����������ԭ�������õ����ķ��������ϵ������˲������Լ�����ʽ�Ľ�����ֱ��ָ������Ҫ��Ϊֹ�������ʵ�ֲ���

���£�

1) �������ù�����С���˷����һ��̶�ʱ�ӵķ������ӳ��˲���[7]������ΪN��ָ����������˲�����Ҫ��ʱ�ӷ�ΧΪ0~1�������㣬������������ﵽ�ľ���ȷ����

2) ����1��P����ʽ��ϱƽ��õ��������˲�����ϵ�������Եõ�N��P����ʽ��ϵ������Щϵ��������1��FARROW�ṹ�ӳ��˲�����

3) ����õ��Ŀɱ�������ӳ��˲���������ָ���Ƿ��꣬������������ɣ�������������ӽ���N�Ͷ���ʽ����P���Ӳ���1)��ʼ���µ�����ƣ�ֱ����Ƶ��˲�����������ָ��Ϊֹ��

ͼ4 ����������ղ���ģ���GNSS�źŲ���ṹ

Fig. 4 Block diagram of proposed implementation for code Doppler compensation within GPS signal acquisition

ͼ5 ����FARROW�ṹ�Ŀɱ�������ӳ��˲�����ʵ�ֽṹ

Fig. 5 Implementation of variable fractional delay filter based on FARROW structure

���ø����ķ����������Ŀɱ�������ӳ��˲������źŲ���Ƶ��Ϊ5 MHz���źŴ���Ϊ��1.023 MHz��ʱ�Ӿ���Ϊ0.01�������㣬���������Ȳ���Ϊ0.1 dB����Ƶõ�������FARROW�ṹ�Ŀɱ��ӳ��˲����ķ�Ƶ���Ժ���Ƶ������ͼ6��ͼ7��ʾ��

��ͼ6��ͼ7���Կ�������Ƴ����Ŀɱ�������ӳ��˲����ķ�Ƶ��Ӧ�Լ�Ⱥʱ�Ӿ�����ͨ����Χ����������Ҫ��

ͼ6 �ɱ������Ⱥʱ����Ӧ����

Fig. 6 Variable fractional delay response

ͼ7 ��Ƶ��Ӧ����

Fig. 7 Magnitude response

2.3 ����������

�ڲ�������������£��������������ղ����Լ���ػ��ֺ�����Ϊ[10]

(13)

(13)

���У�A(f)Ϊ���˲����ķ�Ƶ��Ӧ�� Ϊ���˲�������Ƶ��Ӧ��

Ϊ���˲�������Ƶ��Ӧ�� Ϊ�˲����̶�Ⱥ�ӳ٣�fcΪα�����ʡ���Ӧ��Ƶ����Ӧ����Ϊ

Ϊ�˲����̶�Ⱥ�ӳ٣�fcΪα�����ʡ���Ӧ��Ƶ����Ӧ����Ϊ

(14)

(14)

��������µ���ػ������Ϊ

(15)

(15)

��Ӧ��Ƶ����Ӧ����Ϊ

(16)

(16)

��������ӳ��˲����IJ���������£�

(17)

(17)

ʽ(17)Ϊ���ڷ������ӳ��˲�������IJ�����������Ϊ�������ӳ��˲�����Ƶ�һ��Լ��ָ�ꡣ

��Ӧ����α������ղ���ģ��IJ����IJ���������Ȼ�ܹ�����ʽ(3)��(4)���������У������IJ�������Ҫ����Ϊ��ʽ��

(18)

(18)

3 ��ֵ����

Ϊ���������������������ղ�����������GPS�źŽ��з�����֤�����źŲ����ʵ�ֽṹ��ͼ4��ʾ���ֱ�Ը߶�̬�����ź����������µ�α������ղ������ܽ��з�����֤��������Ҫ�ر�˵�����ǣ�Ϊ�˼����������ĵĸ߶�̬������ָһ��̬������GPS C/A����з�����֤��������Ϊ1.023 Mcps����������Ϊ5 MHz��������þ����ձ��������ػ��ּӷ���ɺ���۵ķ�ʽ�IJ���ṹ��

3.1 �߶�̬�����µ���ķ���

����Դ���������ղ�������������ղ���2������µIJ������ܽ����˷�����֤��������ػ���ʱ��Ϊ5 ms������ɺ���۴���Ϊ10�Σ����ܵĻ���ʱ��Ϊ50 ms����������ͼ8~10��ʾ������ͬ������α���ֵ����Լ����龯�����µļ�����������������նԲ������ܵ�Ӱ�졣��ͼ8�ɼ�����������ճ���33 Hzʱ������IJ�����ij�����6 dB��

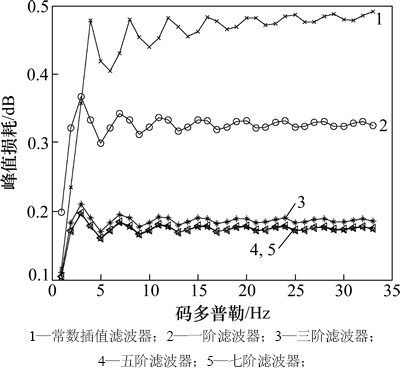

��ͼ9��ͼ10���Կ�������������Ļ���ʱ�ӿ��Ƶ�α������ղ���������һ����Ч��Сα�������Ӱ��Ľ�����������ó�����ֵ�˲��ķ�ʽ��������[5]������������ղ�����ʽ����ֵ��Ŀ��Խ�����0.5 dB���£����������������Ը��ơ������˲������������������������ɵķ�ֵ��ľ�ԽС���������ܸ��Ƶ�Խ���ԡ�����������FARROW�ṹ�������ӳ��˲���ʱ����ֵ��Ŀɽ�����0.2 dB���ҡ���������˲������������ֵ��Ľ��ͺ�С�����ԣ���ʵ��Ӧ����ȡ3���ӳ��˲����DZȽϺõ�һ��ѡ��

ͼ8 ��ͬ������������µ�α���ֵ���

Fig. 8 Correlation peak loss under different code doppler values

ͼ9 ���ÿɱ�������ӳ��˲�������������ղ������α���ֵ���

Fig. 9 Correlation peak losses with code doppler compensated by variable fractional delay filters

ͼ10 ��ͬ����������µļ������

Fig. 10 Detection performance under different C/N0

3.2 ���ź������µ���ķ���

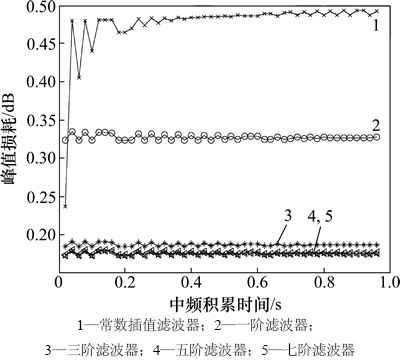

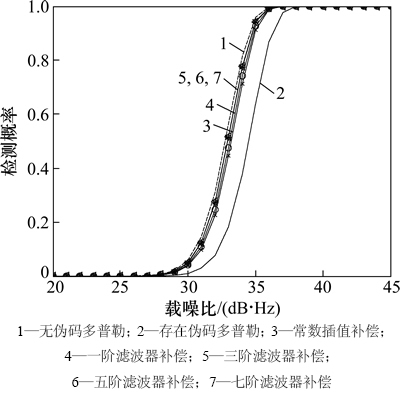

��߶�̬������һ������������ź������´���������ղ�������������ղ���2������µIJ������ܽ��з�����֤������ȡ��ػ���ʱ��Ϊ20 ms���������Ƶ��Ϊ5 Hz������α���ֵ������ܻ���ʱ��ı仯��ϵ����������ͼ2��ͼ9��ʾ������ͬ������α���ֵ����Լ����龯�����µļ�����������������նԲ������ܵ�Ӱ�졣�ӷ��������Կ�����������Ƶ����ʱ��������������������ķ�ֵ���Խ���ԣ����ܻ���ʱ�佫��1sʱ��α���ֵ��ĸߴ�11dB��

ͼ11��ʾΪ����������ղ������α���ֵ�������Ƶ����ʱ��Ĺ�ϵ����ͼ11���Կ�������������Ļ���ʱ�ӿ��Ƶ�������ղ���������һ����Ч��С���ź��������������Ӱ��Ľ�����������ó�����ֵ�˲��ķ�ʽ��ֵ��ĺ߶�̬������һ�����Խ�����0.5 dB���¡����������˲������������������������ɵķ�ֵ��ľ�ԽС������������FARROW�ṹ�������ӳ��˲���ʱ����ֵ���ͬ���ɽ�����0.2 dB���ҡ�

ͼ12��ʾΪ�ܻ���ʱ��Ϊ100 msʱ����������ղ�����IJ������ܡ���ͼ12��ͼ3�Աȿ��Կ���������α������ղ���������ܵõ��˽�����������

ͼ11 ���ÿɱ�������ӳ��˲�������������ղ������α���ֵ���

Fig. 11 Correlation peak losses with code Doppler compensated by variable fractional delay filters

ͼ12 ��ͬ����������µļ������

Fig. 12 Detection performance under different C/N0

4 ����

1) ��һ��̬�����ź������£�������ػ���-����ɺ���۵IJ���ʽ��GPS C/A����з�����֤����һ��̬�����£���ػ���ʱ��Ϊ5 ms������ɺ���۴���Ϊ10�Σ�δ����α������ղ��������£�������մﵽ33 Hzʱ����IJ������Ϊ6 dB�������ź������£���ػ���ʱ��Ϊ20 ms���������Ƶ��Ϊ5 Hz��δ����α������ղ��������£����ܻ���ʱ�佫��1 sʱ��α���ֵ���Ϊ11 dB��

2) ���ñ�������ķ�����2�������µ�α������ս��в��������ó�����ֵ�˲��ķ���ʱ����ֵ��Ľ�����0.5 dB���ң���������FARROW�ṹ�������ӳ��˲���ʱ����ֵ��Ľ�����0.2 dB���ҡ������˲������������������������ɵķ�ֵ���ԽС���������ܸ���Խ���ԡ�

�ο����ף�

[1] Kaplan E D, Hegarty C J. Understanding GPS: Principles and applications[M]. 2nd ed. Boston: Artech House Inc, 2006: 58-61.

[2] James B Y. Tsui Fundamentals of global positioning system receivers: A software approach[M]. New York: John Wiley & Sons, Inc, 2000: 137-138.

[3] Akopain D. Fast FFT based GPS satellite acquisition method[J]. IEE Proc.-Radar Sonar Navigation, 2005, 154: 277-286.

[4] Dafesh P A, Holmes J K. Practical and theoretical tradeoffs of active parallel correlator and passive matched filter acquisition implementations[C]//Proc IAIN World Congress, ION 56th Annual Meeting. San Diego, USA, 2000: 352-362.

[5] ������. �����ܵ������ջ����������㷨��ʵ�ּ����о�[D]. ��ɳ: ������ѧ������ѧ���ӿ�ѧ�빤��ѧԺ, 2011: 46-52.

HUANG Yangbo. Baseband algorithms and implementation tech. for high-performance navigation receiver[D]. Changsha: National University of Defense Technology. Department of Electronic Science and Engineering, 2011: 46-52.

[6] �ϼ. �߶�̬������α��������Լ���Ӧ���о�[D]. ��ɳ: ������ѧ������ѧ, 2005: 37-41.

LI Chunxia. The characteristics of PN code correlation and its applications under high dynamics[D]. Changsha: National University of Defense Technology, 2005: 37-41.

[7] Laakso T I,  V, Karjalainen M, et al. Splitting the unit delay: Tools for fractional delay filter design[J]. IEEE Signal Processing Mag, 1996, 13(1): 30-60.

V, Karjalainen M, et al. Splitting the unit delay: Tools for fractional delay filter design[J]. IEEE Signal Processing Mag, 1996, 13(1): 30-60.

[8] Olkkonen J T, Olkkonen H. Fractional delay filter based on the B-Spline transform[J]. IEEE Signal Process. Lett., 2007, 14(2): 97�C100.

[9] Shyu J J, Pei S C. A generalized approach to the design of variable fractional delay FIR digital filters[J]. Signal Process, 2008, 88(6): 1428-1435.

[10] Pei S C, Lin H S. Tunable FIR and IIR fractional-delay filter design and structure based on complex cepstrum[J]. IEEE Trans Circuits Syst I, 2009, 56(10): 2195�C2206.

[11] Tseng C C, Lee S L. Design of fractional delay filter using weighted hermite interpolation method[J]. IEEE Trans Circuits Syst I, Reg Papers, 2012, 59(7): 1458-1471.

[12] Selva J. An efficient structure for the design of variable fractional delay filters based on the windowing method[J]. IEEE Trans Signal Processing, 2008, 56(8): 3770�C3775.

[13] YA Junyu, XEI Jingxu. Mixed-radix fast filter bank approach for the design of variable digital filters with simultaneously tunable band-edge and fractional delay[J]. IEEE Trans Signal Processing, 2012, 60(1): 100�C111.

[14] Tseng C C, Lee S L. Efficient design and implementation of variable fractional delay filters using differentiators[J]. IEEE Trans Circuits Syst I: Reg Papers, 2011, 58(6): 1311�C1322.

[15] Deng T B, Chivapreecha S, Dejhan K. Bi-minimax design of even order variable fractional-delay FIR digital filters[J]. IEEE Trans Circuits Syst I: Reg Papers, 2012, 59(8): 1766�C1774.

[16] Deng T B. Decoupling minimax design of low-complexity variable fractional-delay FIR digital filters[J]. IEEE Trans Circuits Syst I: Reg Papers. 2011, 58(10): 2398�C2408.

[17] Deng T B. Minimax design of low-complexity even-order variable fractional-delay filters using second-order cone programming[J]. IEEE Trans Circuits Syst II: Exp Briefs, 2011, 58(10): 692-696.

[18] Deng T B. Hybrid structures for low-complexity variable fractional delay FIR filter[J]. IEEE Trans Circuits Syst I: Reg Papers, 2010, 57(4): 897-910.

[19] Shyu J J, Pei S C, Chan C H, et al. A new criterion for the design of variable fractional-delay FIR digital filters[J]. IEEE Trans Circuits Syst. I: Reg Papers, 2010, 57(2): 368�C377.

[20] ������. ���ǵ������ջ��߾��Ƚ�ģ���������Ż�����о�[D]. ��ɳ: ������ѧ������ѧ���ӿ�ѧ�빤��ѧԺ, 2008: 76-80.

XU Xiaoyong. Study on high-precision modeling, analysis and optimization design for satellite navigation receiver[D]. Changsha: National University of Defense Technology. Department of Electronic Science and Engineering, 2008: 76-80.

(�༭ �°���)

�ո����ڣ�2014-06-13�������ڣ�2014-08-20

������Ŀ(Foundation item)��������Ȼ��ѧ����������Ŀ(61403413)(Project (61403413) supported by the National Natural Science Foundation of China)

ͨ�����ߣ�����ά�����о�Ա���������ǵ���ϵͳ��ʱ��ͬ�������о���E-mail��zhuxiangwei@nudt.edu.cn

ժҪ�����ȫ������ϵͳ(GNSS)�źŲ����д���α������գ����һ�ֻ���ʱ�ӿ��Ƶ�α������ղ���������ͨ�������ӳ��˲�����������α�����������ı�����ͽ����źŵ���λ��ƥ�䡣��������������ղ������ڵ��µ�GNSS�źŲ���ṹ������ȫ��λϵͳ(GPS)C/A���źŽ��з�����֤���о�����������ӳ��˲�������Խ��������յIJ���Ч��Խ�ã��ڲ�����Ϊ5 MHzʱ����������Farrow�ṹ�ķ������ӳ��˲���������Ľ�����0.2 dB��