DOI: 10.11817/j.issn.1672-7207.2017.09.019

�ɷ���ת�߾���Ƿѹ�����·���

����1, 2��������1

(1. ������ѧ �ִ������о��� ���� ������710069��

2. �����ʵ��ѧ ���ӹ���ѧԺ������ ������710121)

ժ Ҫ��

�����·(UVLO: Under voltage lockout)����ԭ���Ļ����ϣ�����VIS 0.4 ��m BCD�������һ�־��з���ת���ܵĸ߾���Ƿѹ�����·���õ�·��3������ɣ��Դ�϶�Ƚ���Ϊ���ģ�������г������Եķ���ת��·�Ա�֤Ƿѹ�����ź��ܰ�ȫ�ɿ����������ͨ��������϶�����¶����Ա�֤Ƿѹ������ֵ���ȣ�����Ŵ������·�Ŵ������ȶ���Ƿѹ�����źš�����Cadence����������Ƶĵ�·���з��档�о������������-40~

�ؼ��ʣ�

Ƿѹ����������ת����϶�Ƚ������߾�����BCD������

��ͼ����ţ�TN432 ���ױ�־�룺A ���±�ţ�1672-7207(2017)09-2396-06

Design of high precision undervoltage lockout circuit with function of anti-error flip

TIAN Lei1, 2, JIANG Zhenyi1

(1.

2. School of Electronic Engineering,

Abstract: Based on the analysis of the traditional under voltage lockout theory, a high precision undervoltage lockout circuit with the function of preventing error flip was designed using the

Key words: under voltage lockout; prevent error reversal; bandgap comparator; high precision; BCD process

�ڵ�Դ����оƬ�繦������У������������������������ѹ�����������У�����Դ��ѹ����оƬ������������Χʱ��оƬ�ڲ�ijЩ��·�������������������ܲ����ڲ������Ӷ�ʹ�ⲿ���عܴ��ڲ�ȷ��״̬���п��ܶ��ⲿ��·��оƬ�������ˣ�оƬ�ڲ��������Ƿѹ�����·��Ƿѹ���棬���͵�ѹ���棬�������оƬ�ɿ��ԡ���ȫ�ԣ���оƬ�����ѹ���м�⣬�������Դ��ѹ��Сʱ���ܽ�оƬ����жϣ�ʹоƬ�ڲ�������ȷ���İ�ȫ״̬��ͬʱ������ⲿ���������Ƿѹ�����·����оƬ�������ضϹ��̣����Լ�С�����ⲿ��Դ������оƬ������Ӱ�졣��ͳ��Ƿѹ�����·�����������ѹ������·����ѹ��Դ�����ͱȽ������Լ��ⲿ����ƫ�ã���ʹ��Ƿѹ�����·���Ӹ��ӣ���ͼ�������Ҳ��֮����[1-4]��Ϊ�˿˷���Щ���⣬���������ھ���Ƿѹ����ԭ���Ļ����������һ��Ľ��͵͵�ѹ�����������ܼ��������Դ��ѹ�������и߾��ȴ�϶�ṹ[5-7]�ͷ���ת����[8-9]��Ƿѹ�����·���������о��ȼ��ߵ�Ƿѹ������ֵ�����õ��¶�ϵ��[10-11]���䰲ȫ�ɿ���Ҳ�õ��ܺõı��ϡ�

1 ��·����ԭ����ʵ��

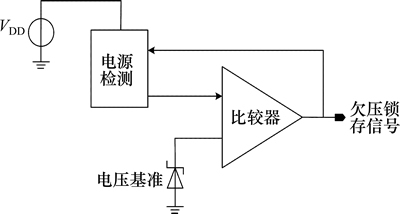

����·�еĵ�Դ��ѹVDD��0��ƽ������ʱ����Դ����·ģ�齫�����仯����������Ͻ�������ֵ�������ıȽ��������ѹ�����бȽϣ�ͬʱ���Ƿѹ�����źţ���оƬ�����ڰ�ȫ״̬[12]�����͵�Ƿѹ�����·�ṹ��ͼ1��ʾ��

ͼ1 Ƿѹ����ԭ��ͼ

Fig. 1 Principle schematic of under voltage lock out circuit

��VDD�մﵽоƬ������ֵʱ���Ƚ���������˴ﵽƽ�⣬���������ת������VDD�������Ƚ��������ƽ������ת��оƬ��������״̬����ʼ��������������ʱǷѹ�����źŷ�������Դ����·���γ��ⲿ������[13-14]����оƬ�ضϹ����У�����VDD���½�����ﵽоƬ�Ĺض���ֵ����ʱ�Ƚ�����������źţ���оƬ������ֱ����Դ��ѹ�½�������оƬֹͣ���������ڱȽ����͵�Դ����·�����������ԣ��γɳ���ЧӦ[15-16]��ʹ��оƬ������ֵ�ض���ֵ��ͬ���������Է�ֹ��Դ��ѹ���ȶ�ʱоƬ��Ƿѹ������ֵ�������Ͽ����ضϡ�

2 �Ľ���ĵ�·ʵ��

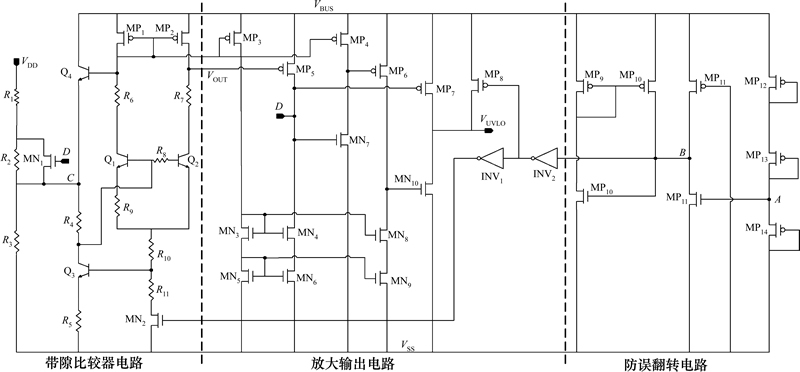

��Դ�ͳǷѹ�����·��ȱ�㣬����˸Ľ��͵ĵ�·�ṹ���Ľ���Ƿѹ�����·��Ҫ�ɷ���ת��·����϶�Ƚ�����·�ͷŴ������·3������ɡ�����ṹ��ͼ2��ʾ��

ͼ2 �Ľ����Ƿѹ�����·

Fig. 2 Improved UVLO circuit

2.1 ����ת��·

�˵�·ʵ��ΪMOS�Ƚ�������MN11�ܵ���ֵ��Ϊ�ο���ƽ����Ҫ�������ڼ���ɵ�Դ��ѹVDD(15~30 V)�������ڲ���ѹ��ԴVBUS(3~5 V)�Ƿ��Ѵﵽ������϶�Ƚ�����·���ȶ���ѹ��ֻ�е�VBUS�ȶ���϶�Ƚ������ܿ�ʼ������Ƿѹ�����źſ�ʼ�������������������ᱻ������MOS��MP12~MP14�Զ��������Ӽ��VBUS����VBUS�ϵ�ʱ��MN11�ضϣ�MP11������B������ߵ�ƽ���������������MN2�ضϣ�MP8�������Ӷ�ʹVUVLO���Ϊ�ߣ�оƬ��������״̬������VBUS��������MN11������B�������͵�ƽ��ͬʱ��MN2������MP8�ضϣ�Ƿѹ�����·��ʼ����������

MP9��MP10��MN10��B�㹹������������MN11������B�㽵�ͣ�MN11��դԴ��ѹVGS�����½�����©�˵���IMN11��֮�½�����MP9����MP10��MN11֧·�����½����ɹ�������ЧӦ��֪B���λ����һ�����ͣ������˷���ת��·������ٶȣ����γɳ���ЧӦ������ֵV+�ļ���(VBUS������)Ϊ��

(1)

(1)

(2)

(2)

(3)

(3)

(4)

(4)

���У�VGS11=V+/3��VGS10=VDS=Vinv(��������ת����)����=��Cox(W/L)��������

(5)

(5)

(6)

(6)

����ʵ�ʵ�VBUS��ȡ������Χ�ڵĽ⡣

(7)

(7)

(8)

(8)

(9)

(9)

����ֵV-�ļ��㷽��������ֵ��ͬ��ֻ��������״̬�ı��෴��

2.2 ��϶�Ƚ�����·

VBUS�ȶ���϶�Ƚ���������MN2��Ϊ���عܣ��䵼ͨ��VDS��ѹ���Ժ��Բ��ƣ�����Ե�ԴVDD��ѹ��������Q1��Q2�����ṩƫ�ã��������ο���ѹ�����ݴ�϶��������ԭ����Q1���伫���ΪQ2��4������Q1��Q2��R9����PTAT����IQ1��gm1��

(10)

(10)

(11)

(11)

����gm2R9>>1������Gm1��Gm2����Q1���缫����IQ1�仯��С��Q2���缫����IQ2�仯�ʡ���VDD��Сʱ��IQ1��IQ2��ͨ��������MP1����MP2��PTAT����С��IQ2��Q2֧·Ϊ�˴ﵽƽ�⣬MP2������������VOUT������ߵ�ƽ��

����VDD���ߣ�Q1������λҲ�����ߣ�ijһʱ��Q1��Q2֧·���ﵽ������ȵ�״̬��VOUT�Ա��ָߵ�ƽ����ʱQ1������ѹΪ

(12)

(12)

ͼ2��������Q3��Q4��R4���ɶԻ���ѹVref�Ķ����¶Ȳ�����R8���ڻ�����������С����������Q1��Q2���缫֧·������Ӱ�졣���¶�T���£�Q3�ضϣ�C���λ������ѹVref�������¶�������Q3�������������¶�ϵ������IQ3����������R4��Vref���ӵõ����������ѹ���¶�ϵ����

(13)

(13)

(14)

(14)

(15)

(15)

ֻ���������R4��R5��R9~R11���ɸĽ�����ѹ���¶����ԡ�

��VDD�������ߺ�IQ1��IQ2��MP1����MP2��PTAT��������IQ2��Ϊ�˴ﵽƽ�⣬MP2�����뱥������VOUT���Ϊ�ͣ�ͬʱVUVLO������ת���ɼ�����ʱ���Ϸ�ת��ֵ��ѹV+��

�����ѹ�õ���C���ѹ��

(16)

(16)

��ʽ(14)����ʽ(16)�ã�

(17)

(17)

��VDD�ﵽ����ת��ֵ��D��MP5©�˵�ѹ���Ϊ�ߣ����ع�MN1������������R2��·����ʱC���ѹΪ

��

�� (18)

(18)

����VC���ӿ���Ƿѹ�źŷ�ת���ٶȣ������·Ϊ��������ͬʱ�γ��˳��͡�ͬ������VDD�½��Ĺ����У��·�ת��ֵV_Ϊ

(19)

(19)

��������Ϊ

(20)

(20)

2.3 �Ŵ������·

��϶�Ƚ��������Ƿѹ�����ź�(VOUT)�п�����ڷ�̫С����ʹ����Ѹ�ٿ����ضϣ�������ӷŴ�������DZ�Ҫ�ġ���ͼ2��֪���˲��ֿ��Կ���������Դ����һ���������������Ҫ��MP5~MP7��MN7��MN10��ɶԴ�϶�Ƚ������Ƿѹ�ź�VOUT�ķŴ���̡�

��VDD����δ�ﵽ����ֵǰ��VOUT���Ϊ�ߣ�D���λΪ�ͣ�MP5��MN7��MP6��MN10�ѹضϣ���ʱMP7���ڿ���״̬����VUVLO��������ߵ�ƽVBUS��

��VDD�ﵽ����ֵ��VOUT����ɸ߱�ͣ�MP5��������D���������ߵ�ƽVBUS������R2����·��������MN7��MP6��MN10����������ʱMP7���ضϣ�VUVLO����ɸ߱�ͣ�оƬ����Ƿѹ����״̬��

��������ֵ������ֵ���г����������VDD�����½�����������ֵ��VUVLO���ܷ�ת����ʱVOUT����ɵͱ�ߣ���MP5�ضϣ�D�㱻�������أ��Ӷ�����MP7��MN7��MP6��MN10�����ڹض�״̬�����VUVLO������Ϊ�ߣ�һֱ������оƬ�رա�

3 ��·�����������

3.1 ������

������Ƶ�Ƿѹ�����·��Ӧ���ڵ�Դ������Χ��-0.3~20 V��PFC����оƬ�У�Ϊ�˸��õ���Ƹ���ָ�꣬������ԸĽ��ĵ�·��ģ�����Cadence���з�����֤������ģ�Ͳ���VIS 0.4 ��m BCD���յĵ���������¶���Ϊ-40~

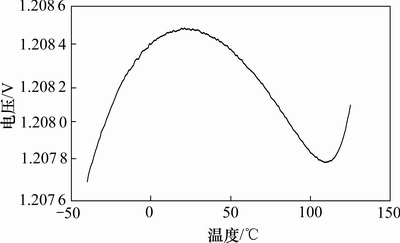

��ͼ3�ɼ�������ѹ���������¶Ȳ������ȶ���1.208 V�������¶�ϵ���ɴﵽ5��10-6 ��-1���ܹ�Ϊ�ıȽ����ṩ�ȶ���ȷ�IJο���λ��������֤Ƿѹ�����·��ֵ��ѹ���ȶ������

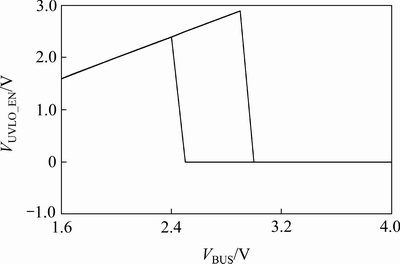

Ϊ��ȷ��Ƿѹ�����·������źŰ�ȫ�����ĶԺķ�ֹ��ת��·���з��棬��ֱ������������ͼ4��ʾ��ͼ��VBUS��оƬ�ڲ�����ѹ��Դ����������Ϊ3~5 V����ʵ�ʹ����У����õ͵�ѹ������Լ�СоƬ���ĺ�Ƿѹ������ֵ��ƫ����ԣ�����ת��·ֻ����VBUS�ȶ�����ʱʹ����������������ɣ���������������ֵΪ2.95 V������ֵΪ2.5 V����������ȷ��Ƿѹ�����·��ȫ�����

ͼ3 ��϶�Ƚ�������ѹ�¶���������

Fig. 3 Temperature characteristic curve of bandgap reference voltage comparator

ͼ4 ����ת��·��ֱ����������

Fig. 4 DC characteristic curve of error flip circuit

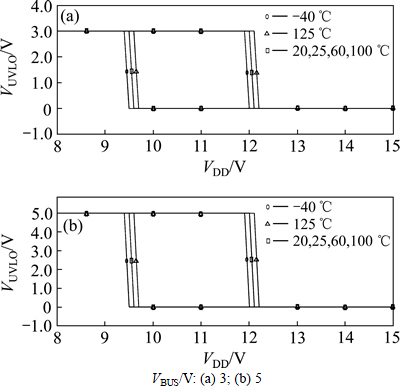

Ϊ��ȷ��Ƿѹ�����·����źŵ��¶����ԣ��ֱ��ڲ�ͬ��ѹ������£��¶�ȡ-40��-20��25��60��100��

����Դ��ѹVDDѡΪ8~15 Vʱ���ɿ���

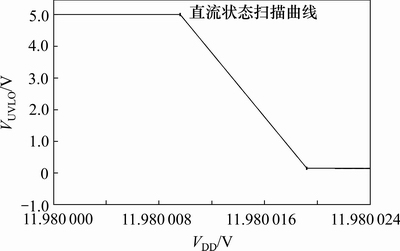

��ͼ6�ɼ���VDD��11.980 010 VʱVUVLOΪ�ߣ���VDD�ﵽ11.980 021 Vʱ��VUVLO��ͣ��ֱ���Ϊ0.01 mV��������ȫ�����·Ҫ��

ͼ5 ��ͬ�¶���Ƿѹ�������ֱ������

Fig. 5 DC curves of UVLO at different temperatures

ͼ6 Ƿѹ������ֵ���ȷ�������

Fig. 6 Simulation result of UVLO threshold accuracy

3.2 ʵ�������

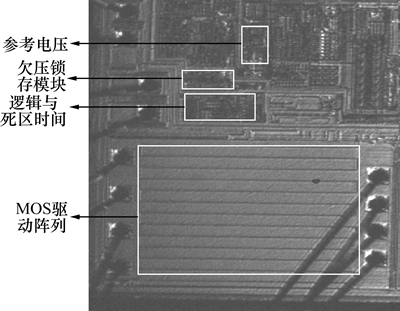

ͼ7��ʾΪ�����оƬ������Ƭ����Ƭ������Ϊ1 313 ��m��878 ��m������Ƿѹ����ģ��λ����ͼ7��ʾ��

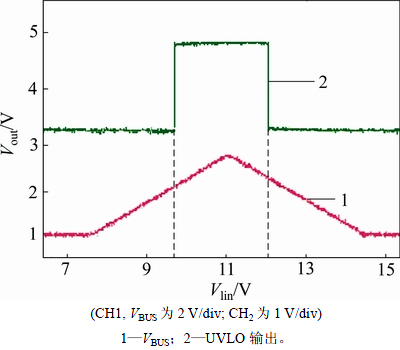

ʹ��̩��(Tektronix)TDS5104Bʾ��������Ƭ���оƬ���в��ԡ���оƬ�ڲ������ѹΪ3~5 Vʱ��ʵ������ͼ8��ʾ��

ͼ8�У��ϵ��ʼʱ�̣�VBUSС����ֵ����ʱ��оƬ������źź�Ϊ���͵�ƽ����VBUS����������ֵ��UVLO����ߵ�ƽ��оƬ���������������ʼʱ�̣�VBUS��������ֵʱ��оƬ�Կ��������������½�������ֵ��UVLO����͵�ƽ��оƬ���������ɴ˿��Կ�����ʵ��������������Ǻϣ���������оƬʵ�ʹ���������

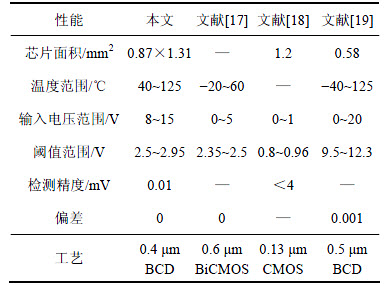

��1��ʾΪ������Ƶĸ߾���Ƿѹ�����·ģ��������[17-19]�е�Ƿѹ�����·���ܲ����ıȽϽ�����ɱ�1���Կ�������������Ƶ�Ƿѹ�����·���нϸߵľ��ȡ�

ͼ7 оƬ������Ƭ

Fig. 7 Microphotograph of chip

ͼ8 Ƿѹ��������ʵ�Ⲩ��

Fig. 8 Test result of UVLO characteristic

��1 UVLOģ������ܶԱ�

Table 1 Comparative results of characteristic in UVLO module

�ɴ˿ɼ���������Ƶ�Ƿѹ�����·���о��ȸߣ�ƫ��С���ص㣬���Ա����·����������ܹ���ȫ���㿪�ص�Դ�����ĵ�·Ҫ��

4 ����

1) ��Կ��ص�Դϵͳ�б����Ƿѹ���湦�ܣ��ڴ�ͳ���۵Ļ����������һ��Ľ��;��з���ת���ܵĸ߾���Ƿѹ�����·���õ�·���Թ�����3~5 V��ѹ�¼��10~30 V�ĵ�Դ��ѹ����������ֵʧ�棬���ô�϶�Ƚ�����ʹ��Ƿѹ������ֵ���ȿɴ�10-5 V���Ҿ������õ��¶��ȶ��ԣ���

2) �������ת��·��֤Ƿѹ�����ź����ڹ�����ѹ�ȶ����������Ƿѹ�����·�������պ������ߴ������Ӧ���ڸ��ֵ�ԴоƬ�С�

�ο����ף�

[1] ��ѩ��, ������. һ�ֻ��ڱ���������Ƿѹ������·����ƺ�ʵ��[J]. ���пƼ���ѧѧ��(��Ȼ��ѧ��), 2007, 35(10): 64-66.

ZOU Xuecheng, HAN Junfeng. Design and implementation of an undervoltage lockout circuit base on proportional current[J]. Journal of

[2] LIN R L, YEH P Y, LIU C J H. Positive feed-forward control scheme for distributed power conversion system with multiple voltage sources[J]. IEEE Transactions on Power Electronics, 2012, 27(7): 3186-3194.

[3] WU Xiaobo, ZHANG Yongliang, ZHANG Danyan, et al. Design of a monolithic hot swap controller IC with BCD technology[J]. Chinese Journal of Semiconductors, 2006, 27(5): 948-954.

[4] WOOD P N. Monolithic level-shifting MOS gate drivers cut parts count while providing added control functions[J]. Power conversion and Intelligent Motion, 1994, 20(8): 40-44.

[5] SHEN Z J, SABUI G, MIAO Zhenyu, et al. Wide-bandgap solid-state circuit breakers for DC power systems[J]. IEEE Transactions on Device and Circuit Considerations in Electron Devices, 2015, 62(2): 294-300.

[6] OSAKI Y, HIROSE T, KUROKI N, et al. 1.2 V supply, 100 nW, 1.09 V bandgap and 0.7 V supply, 52.5 nW, 0.55 V subbandgap reference circuits for nanowatt CMOS LSIs[J]. IEEE Journal of Solid-State Circuits, 2013, 48(6): 1530-1538.

[7] ZHANG Hualei, XIAO Zhibin, XI Tan, et al. Low-power sub-1-V compact bandgap reference for passive RFID tags[J]. Electronics Letters, 2015, 51(11): 815-816.

[8] CHUANG Y L, KIM S M, SHIN Y S, et al. Pulsed- latch aware placement for timing-integrity optimization[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(12): 1856-1869.

[9] LUO Yinhong, ZHANG Fengqi, GUO Hongxia, et al. Single-event cluster multibit upsets due to localized latch-up in a 90 nm COTS SRAM containing SEL mitigation design[J]. IEEE Transactions on Nuclear Science, 2014, 61(4): 1918-1923.

[10] LI Jinghu, ZHANG Xingbao, YU Mingyan. A 1.2 V piecewise curvature-corrected bandgap reference in 0.5 ��m CMOS process[J]. IEEE Transactions on Very Large Scale Integration Systems, 2011, 19(6): 1118-1122.

[11] ZHOU Zekun, YUE Shi, ZHI Huang, et al. A 1.6 V 25 ��A 5 ppm/�� curvature-compensated bandgap reference[J]. IEEE Transactions on Circuits and Systems ��: Regular Papers, 2012, 59(4): 677-684.

[12] ��ѧ��, �ܼ̳�, ֣��ǿ. һ�ֻ��ڵ�ƽλ�Ƶ�·�ĵ͵�ѹȫ�ڷ�CMOS�˷�[J]. ���ϴ�ѧѧ��(��Ȼ��ѧ��), 2010, 41(4): 1473-1477.

PAN Xuewen, ZHOU Jicheng, ZHENG Xuqiang. A level-shifting circuit based on low-voltage rail-to-rail CMOS op-amp[J]. Journal of

[13] TIAN Lei, LAI Xinquan. Symmetrical structure strong drive capability optocoupler sensor[J]. Sensors and Transducers, 2013, 159(11): 319-323.

[14] ZHANG Yunwu, ZHU Jing, SUN Weifeng. A novel UVLO circuit with current-mode control technique for DC-DC converters[J]. Advanced Information and Computer Technology in Engineering and Manufacturing, Environmental Engineering, 2013, 765/766/767: 2534-2537.

[15] ANVARIFARD M K, OROUJI A A. Improvement of electrical properties in a novel partially depleted SOI MOSFET with emphasizing on the hysteresis effect[J]. IEEE Transactions on Electron Devices, 2013, 60(10): 3310-3317.

[16] RODRIGUES C R, MULLER C, MONTEIRO NETO D J. Hysteresis settling technique for CMOS comparators based on substrate voltage[J]. Electronics Letters, 2013, 49(1): 27-28.

[17] ���, ����, ����, ��. һ�ָĽ���BiCMOS����Ƿѹ�����·�����[J]. �ִ����Ӽ���, 2007, 24(3): 182-184.

WANG Jin, TIAN Ze, LI Pan, et al. Design of an improved under voltage lock out circuit based on BiCMOS process[J]. Modern Electronics Technique, 2007, 24(3): 182-184.

[18] ����ӱ, ������, ����, ��. һ������������SoC���ϵ縴λ��Ƿѹ����·[J]. ����ѧ, 2015, 45(5): 607-610, 614.

CHEN Chengying, CHEN Liming, FAN Jun, et al. A power- on-reset and brown-out circuit for hearing-aid SoC[J]. Microelectronics, 2015, 45(5): 607-610, 614.

[19] ZHAO Y R, LAI X Q. Novel bandgap-based under-voltage- lockout methods with high reliability[J]. Journal of Semiconductors, 2013, 34(10): 105008-1-8.

(�༭ �Կ�)

�ո����ڣ�2016-09-28�������ڣ�2016-12-13

������Ŀ(Foundation item)������ʡ������ר����мƻ���Ŀ(15JK1676)������������ѧ�滮�����ص�������Ŀ(2015EA03)�������ʵ��ѧ�����ʦ�����ص�������Ŀ(101-0488) (Project(15JK1676) supported by the Shaanxi Provincial Department of Education Scientific Research of China; Project(21015EA03) supported by Key Project of Social Science Planning of Xi��an City; Project(101-0488) supported by the Youth Founded Project of Xi��an University of Posts and Telecommunications)

ͨ�����ߣ����ڣ���ʿ��ʦ�����µ�ԴоƬ����缯�ɵ�·���о���E-mail: tianlei@xupt.edu.cn

ժҪ���ڷ�����ͳǷѹ�����·(UVLO: Under voltage lockout)����ԭ���Ļ����ϣ�����VIS 0.4 ��m BCD�������һ�־��з���ת���ܵĸ߾���Ƿѹ�����·���õ�·��3������ɣ��Դ�϶�Ƚ���Ϊ���ģ�������г������Եķ���ת��·�Ա�֤Ƿѹ�����ź��ܰ�ȫ�ɿ����������ͨ��������϶�����¶����Ա�֤Ƿѹ������ֵ���ȣ�����Ŵ������·�Ŵ������ȶ���Ƿѹ�����źš�����Cadence����������Ƶĵ�·���з��档�о������������-40~