用于GPS卫星导航系统的低噪声放大器设计

项勇1,周仁杰1,段炼1,甘业兵1, 2, 3,马成炎1, 2, 3,叶甜春1

(1. 中国科学院 微电子研究所,北京,100029;

2. 杭州中科微电子有限公司,浙江 杭州,310053;

3. 嘉兴联星微电子有限公司,浙江 嘉兴,314000)

摘要:采用0.18 μm SiGe BiCMOS工艺设计一个用于GPS卫星导航系统射频前端电路的低噪声放大器。该低噪声放大器采用BiFET(Bipolar-MOSFET) Cascode结构可以同时实现极低噪声和高线性度。采用异质结晶体管(heterogenous bipolar transistor, HBT)作为输入管以提供低噪声性能,Cascode级采用MOSFET管来提高线性度。与传统的全HBT管或全MOSFET管相比,这种混合结构能更方便地实现噪声、增益和线性度之间的折中设计。当该低噪声放大器在2.85 V电源电压下工作时,消耗3.7 mA电流,提供19 dB功率增益,噪声系数为0.9 dB,输入1 dB压缩点为0.065 mW。

关键词:低噪声放大器;噪声系数;BiFET Cascode结构;线性度

中图分类号:TN772 文献标志码:A 文章编号:1672-7207(2013)11-4513-07

Design of low noise amplifier for GPS receiver

XIANG Yong1, ZHOU Renjie1, DUAN Lian1, GAN Yebing1, 2, 3, MA Chenyan1, 2, 3, YE Tianchun1

(1. Institute of Microelectronics, The Chinese Academy of Science, Beijing 100029, China;

2. Hangzhou Zhongke Microelectronics Co. Ltd., Hangzhou 310053, China;

3. Jiaxing Lianxing Microelectronics Co. Ltd., Jiaxing 314000, China)

Abstract: The design and implementation of a low noise amplifier (LNA) based on 0.18 μm SiGe BiCMOS process for the RF circuits in GPS receivers was presented. It uses a BiFET Cascode structure and achieves ultra low noise and considerable linearity simultaneously. The heterogenous bipolar transistor (HBT) input transistor provides very low noise and a cascode MOSFET enhances the linearity. With the use of this mixed approach, it is easier to realize the trade-off between gain, noise figure, linearity and power consumption than the conventional full-HBT or full-MOSFET structures. The LNA consumes total 3.7 mA current under 2.85 V supply voltage and results in a simulated noise figure(NF) of 0.9 dB, a power gain of 19 dB, a input 1 dB compression power(ICP1) of 0.065 mW.

Key words: LNA; noise figure; BiFET Cascode; linearity

低噪声放大器(low noise amplifier,LNA)作为射频接收机的最前端模块,其噪声性能直接决定了整个接收机的噪声系数[1-3],从而影响接收机系统的接收灵敏度。低噪声放大器除了尽可能地引入低噪声之外,还要求提供一定的功率增益以抑制后级模块噪声对整个接收机噪声性能的影响,良好的输入输出阻抗匹配特性以降低信号在传输过程中的功率损耗[4],具有较高的线性度以避免非线性对信号质量的影响。随着近几年的快速发展,SiGe BiCMOS工艺以其高频特性好、噪声极低、工艺集成度高等优点被广泛应用于射频通讯领域[5-7],特别是应用于单片集成低噪声放大器的设计。GPS卫星导航系统作为目前全球应用最广泛的卫星导航系统,其性能要求也在不断寻求突破,特别是GPS接收机的接收灵敏度,而接收灵敏度通常由射频前端低噪声放大器的噪声系数决定,因此,研究减小低噪声放大器的噪声系数对于提高GPS接收机的接收灵敏度具有重要的实际意义。发射极简并电感型共射放大器是目前应用最广的一种低噪声放大器结构[8-10],它利用发射极简并电感来得到具有正实部的输入阻抗,并在功耗受限的情况下获得较优的噪声性能。为了消除有限的输出阻抗和密勒效应的影响,Cascode技术也被普遍采用,同时Cascode技术还能增强低噪声放大器的反向隔离度[11]。在恶劣的工作环境中,由于接收到的信号动态范围很大,接收机很容易被强信号阻塞造成后级混频器过早陷入饱和,这样就对低噪声放大器的线性度提出了很高的要求。众所周知,线性度的提高是需要以增益降低、噪声恶化、功耗增加为代价的[4, 8],因此,如何在高增益、低噪声、高线性度、低功耗之间进行折中是目前低噪声放大器设计面临的主要挑战。传统的SiGe工艺低噪声放大器采用纯HBT管来实现,尽管可以获得很低的噪声系数,但是,线性度在一定程度上受到了较大限制。为了设计一个能同时提供低噪声性能和高线性度的低噪声放大器,本文作者采用BiFET(Bipolar-MOSFET) Cascode结构,利用异质结晶体管(HBT)的噪声低和MOSFET管线性度好的特点,以同时获取低噪声性能和高线性度。输入级采用先进的噪声优化策略既能使噪声最小又能满足输入阻抗匹配的要求,MOSFET管作为Cascode级提高了整个结构的线性度,通过优化MOSFET管的尺寸和偏置条件可以获得最佳的线性度性能。

1 BiFET LNA设计理论和电路优化

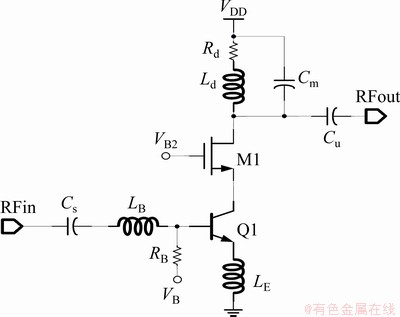

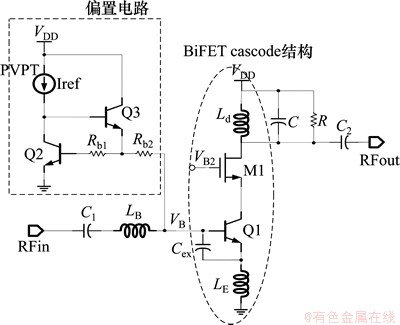

BiFET cascode结构采用HBT管和MOSFET管结合的方式[11],综合了BiCMOS工艺中2种类型管子各自的优良特性:HBT管截止频率fT高,噪声低,适合做输入级;MOSFET管线性度好,适合做Cascode级。与HBT-HBT或MOS-MOS的结构相比,该结构能够在高增益、低噪声、高线性度和低功耗之间进行更好地设计。BiFET LNA拓扑结构如图1所示。HBT管输入共射极放大器Q1作为输入级提供低噪声和良好的输入阻抗匹配,MOSFET管M1作为Cascode级减小Q1引起的密勒效应,提高增益,增加反向隔离度和提供良好的线性度。BiFET LNA的设计过程和优化采用文献[11]中的设计方法和步骤。

图1 BiFET LNA拓扑结构

Fig.1 Topology structure of BiFET LNA

1.1 输入级噪声优化与阻抗匹配

Cascode结构LNA的噪声性能主要由输入共射极放大器(Q1)的噪声决定。为了获取最小的噪声,设计输入管Q1时,必须尽可能地使信号源阻抗接近其最佳噪声匹配阻抗[12]。但是,通常该最佳噪声匹配阻抗与信号源阻抗(如50Ω)不相同[1],不可能同时达到最优噪声性能和完全阻抗匹配。因此,输入级设计的重点就是在一定的阻抗匹配条件下使其噪声性能尽量接近最优噪声匹配点。本文采用文献[12]提出的功率约束下的输入阻抗匹配、噪声优化策略,这种优化策略在低功耗应用中具有更重要的实用意义。

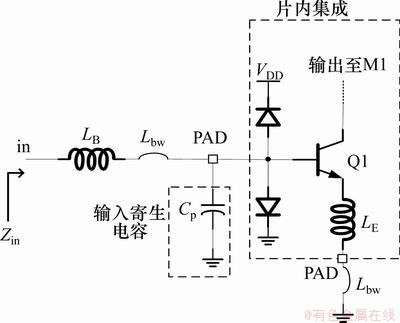

带ESD防护和封装PAD的输入级简化电路如图2所示。图2中:LB为片外输入串联电感;LE为发射极简并电感,Lbw为封装打线寄生电感;Cp为输入端寄生电容,包括封装寄生电容、ESD寄生电容和Q1的密勒电容。

忽略输入寄生电容Cp时,输入阻抗可以表示为

(1)

(1)

式中:rB和rE分别为Q1的基极电阻和发射极电阻; 为Q1的基极-发射极之间的结电容;

为Q1的基极-发射极之间的结电容; 为Q1的单位电流增益特征频率;

为Q1的单位电流增益特征频率; ,

, 。

。

在谐振频率 ,输入阻抗的虚部为0Ω,表现为纯实数阻抗:

,输入阻抗的虚部为0Ω,表现为纯实数阻抗:

(2)

(2)

若考虑输入寄生电容Cp的影响[13],则输入阻抗的实部变为:

(3)

(3)

Cp会降低输入阻抗的实部,因此,对于50Ω的源阻抗来说,在Q1的设计时应使Req大于50Ω以补偿Cp造成的影响[14]。

图2 带ESD防护和封装的输入级

Fig.2 ESD protected LNA with package pads

HBT管的噪声性能取决于2个重要参数:最小噪声系数Fmin[15-16]和噪声电阻Rn。Fmin决定了HBT管所能达到的最小噪声,Rn反映了实际噪声系数F与Fmin的偏离程度,其表达式如下:

(4)

(4)

(5)

(5)

其中: 为直流下集电极与基极的电流增益;n为工艺参数(通常取值为1~1.2);(rB+rE)u为表示单位面积的基极电阻和集电极电阻之和;JC为HBT管集电极的电流密度;AE为HBT管的发射极面积;VT为热电压(

为直流下集电极与基极的电流增益;n为工艺参数(通常取值为1~1.2);(rB+rE)u为表示单位面积的基极电阻和集电极电阻之和;JC为HBT管集电极的电流密度;AE为HBT管的发射极面积;VT为热电压( );

); 和

和 分别为工作频率和特征频率。

分别为工作频率和特征频率。

由式(4)和(5)可知,为获得最佳的噪声性能,应采用 大、

大、 高、rB+rE小的HBT管[17-19]。由于

高、rB+rE小的HBT管[17-19]。由于 与JC有关,因此,需要对JC进行优化,使得Fmin尽量小。对于特定的工艺,借助计算机辅助仿真或测试是获取最优JCopt的有效方法[2]。本设计采用华虹HHNEC 0.18 μm SiGe RF BiCMOS工艺,在一定尺寸条件下,HBT管的Fmin随JC变化的情况如图3所示。仿真结果显示,在工作频率为1.575 GHz时,最优电流密度JCopt为100 μA/μm2 (图3的A点),此时Fmin达到0.453 dB。

与JC有关,因此,需要对JC进行优化,使得Fmin尽量小。对于特定的工艺,借助计算机辅助仿真或测试是获取最优JCopt的有效方法[2]。本设计采用华虹HHNEC 0.18 μm SiGe RF BiCMOS工艺,在一定尺寸条件下,HBT管的Fmin随JC变化的情况如图3所示。仿真结果显示,在工作频率为1.575 GHz时,最优电流密度JCopt为100 μA/μm2 (图3的A点),此时Fmin达到0.453 dB。

图3 最小噪声系数随电流密度的变化关系

Fig.3 Minimum NF versus current density

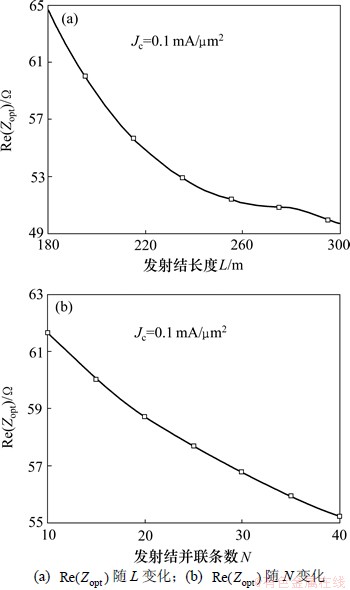

确定了管子的最优电流密度JCopt以后,通过调整HBT管子的发射结面积(包括发射结总长度L和并联个数N)使得最佳噪声源阻抗的实部等于50Ω以满足噪声匹配[2],即 =50Ω。在保持电流密度不变的情况下,

=50Ω。在保持电流密度不变的情况下, 随发射结总长度L和并联条数N的变化关系如图4所示。总的来说,

随发射结总长度L和并联条数N的变化关系如图4所示。总的来说, 随着发射结总长度L增大而减小,但是如果L过大,会导致电流IC大大超过功耗预算,因此,需要合理选择L使

随着发射结总长度L增大而减小,但是如果L过大,会导致电流IC大大超过功耗预算,因此,需要合理选择L使 在功耗限制范围内尽量接近50Ω。并联条数N增加会减小

在功耗限制范围内尽量接近50Ω。并联条数N增加会减小 ,因此,可以调整并联条数N以使

,因此,可以调整并联条数N以使 进一步靠近50Ω。

进一步靠近50Ω。

确定管子Q1的电流密度JC、发射结总长度L和发射结并联条数N以后,其特征频率 为

为

(6)

(6)

其中: 为管子Q1的跨导;

为管子Q1的跨导; 为Q1的基极-发射极之间的结电容。

为Q1的基极-发射极之间的结电容。

由式(2)可知,输入阻抗匹配到50Ω时,射极简并电感LE由下式确定:

(7)

(7)

其中:RS为信号源阻抗50Ω。根据电路的工作频率 ,片外输入串联电感LB为

,片外输入串联电感LB为

(8)

(8)

至此,已完成了输入级的全部设计,实现了功率约束下的噪声匹配和阻抗匹配,同时获得了低噪声性能和良好的输入阻抗匹配。

图4 噪声匹配源阻抗实部 与发射结总长度L和发射结并联条数N的关系

与发射结总长度L和发射结并联条数N的关系

Fig.4  versus emitter length L and emitter stripe number N

versus emitter length L and emitter stripe number N

1.2 Cascode级MOSFET管的设计

在电流相同条件下,为了能够提供更好的线性度,采用MOSFET管取代传统的HBT管作为Cascode级。若要MOSFET管既能获得最好的线性度,又能提供可观的增益,则必须对MOSFET管的尺寸进行优化。MOSFET管的宽度W由式(9)决定[11]。

(9)

(9)

其中:IC为输入级确定的工作电流;CBC为输入级Q1管基极-集电极结电容; 和COX为MOSFET管的工艺参数;L为MOSFET管的沟道长度;f0为BiFET LNA的工作频率,必须满足

和COX为MOSFET管的工艺参数;L为MOSFET管的沟道长度;f0为BiFET LNA的工作频率,必须满足

f0≤ (10)

(10)

由式(10)可知:大偏置电流IC、小结电容CBC和尽量短的沟道长度L对保证BiFET LNA的高频特性非常重要[11]。IC和CBC通常由输入级决定,因此,在实际设计中沟道长度通常取工艺的最小沟道长度,MOSFET的宽度由式(9)计算得到。

2 BiFET LNA电路设计和实现

本文设计的BiFET LNA在华虹HHNEC公司的0.18 μm SiGe BiCMOS工艺上实现,其整体电路如图5所示。由电流源Iref,HBT管Q2和Q3以及电阻Rb1和Rb2组成偏置电路,为输入管Q1提供偏置电流,Iref为PVPT基准电流源。HBT管Q1和MOSFET管M1构成BiFET Cascode结构。电感Ld、电容C构成负载谐振网络,R并联在谐振网络中,用于降低谐振网络Q值,增加带宽和稳定性。电容C2用于隔直和输出匹配。电感LB和LE用于输入阻抗匹配。电容Cex用来减小输入寄生电容的影响,增加设计自由度。

图5 本文的BiFET LNA电路原理图

Fig.5 Schematic of designed BiFET LNA

(1) HBT管输入级与阻抗匹配网络。根据功率约束下噪声匹配/阻抗匹配设计的方法,输入管Q1采用40个并联条、每条长度为2 μm的发射结,偏置电流IC=3.5 mA。在1.575 GHz下,匹配网络各元件的取值为:LE=0.8 nH,LB=6.8 nH,Cex=100 fF。

(2) Cascode级。确定电流IC=3.5 mA,Q1管的CBC=50 fF,采用最小沟道长度Lmin=0.18 μm, 和

和 均可从工艺参数中得到,根据式(9)计算得到最佳宽度Wopt=120 μm。

均可从工艺参数中得到,根据式(9)计算得到最佳宽度Wopt=120 μm。

(3) 负载和输出匹配。工作频率为1.575 GHz,各元件参数如下:Ld=6.1 nH,C=0.7 pF,R=1.54 kΩ,C2=0.66 pF。

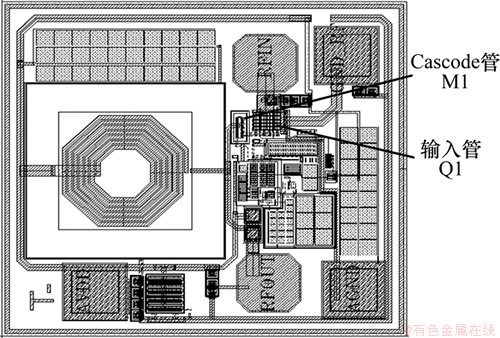

本文所设计的BiFET LNA整体版图如图6所示,包括基准电流源、偏置电路和BiFET LNA主电路以及ESD保护电路、射频输入输出PAD和电源PAD。输入管Q1采用多个条状并联的发射极,并打上尽量多的接触孔以减小基极寄生电阻来优化噪声。Q1应摆放在距离输入PAD尽可能近的地方,并且连线采用高层金属线以减小寄生电阻和寄生电容。电源和地之间填充大量的电容以确保电路的稳定性。版图的总体长×宽为0.54 mm×0.58 mm。

图6 BiFET LNA的整体版图

Fig.6 Layout of designed BiFET LNA

3 仿真结果与分析

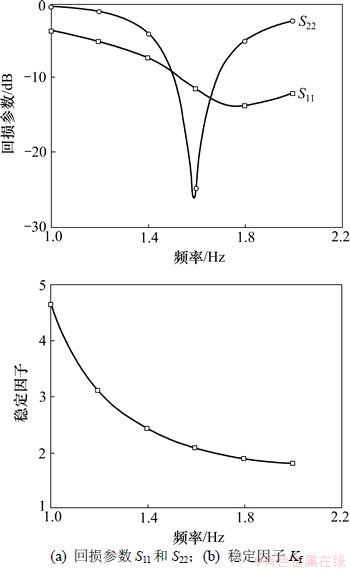

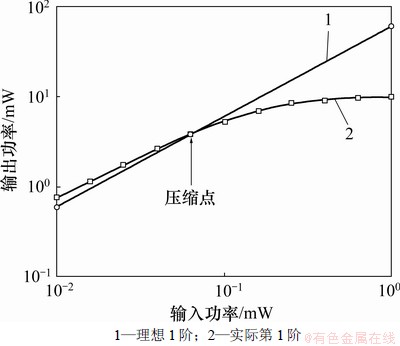

本文设计的BiFET LNA工作在2.85 V电源电压下,总电流为3.7 mA,其中BiFET LNA主电路消耗3.5 mA,偏置电路消耗0.2 mA。将版图寄生参数和封装寄生参数考虑在内,用Cadence Spectre RF对该BiFET LNA的S参数(S11,S21,S22,S12)、噪声系数F、输入1 dB压缩点ICP1、稳定因子Kf等指标进行仿真,结果如图7~9所示。

图7 F和S21随频率变化仿真曲线

Fig.7 Simulated F and S21 versus frequency

图8 S11,S22和Kf随频率变化仿真曲线

Fig.8 Simulated S11, S22 and Kf versus frequency

图9 输入1 dB压缩点仿真曲线

Fig.9 Simulated input 1 dB compression point (single-tone)

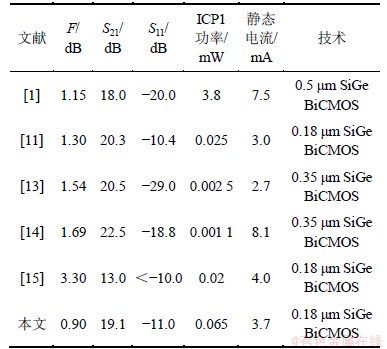

噪声系数F随频率的变化曲线如图7(a)所示,在1.575 GHz频率点F为0.9 dB,直到2 GHz时F仍小于1.0 dB,说明本文采用的噪声优化策略在GPS频段范围内的应用有效。同时,与本文前面得出的最小噪声系数0.45 dB相比,噪声系数较高,这主要是由片内电感的寄生电阻、版图寄生、封装寄生等非理想因素造成的。仿真S21随频率的变化曲线如图7(b)所示。从图7(b)可见:在1.575 GHz频率点功率增益S21为19.1 dB,1 dB带宽大约为260 MHz,与纯HBT结构相比,功率增益有所降低,这主要是由Cascode MOSFET管增益不足引起的,但对于GPS系统应用来说,19 dB增益已经足够。图8(a)所示为S11和S22随频率的变化曲线,在1.575 GHz频率点S11<-11 dB,S22<-23 dB,均符合回损小于-10 dB要求。Kf随频率的变化曲线如图8(b)所示,Kf=2.1(频率为1.575 GHz),且在全部工作频段范围内Kf>1,说明该LNA是无条件稳定的。LNA的线性度可以通过输入1 dB压缩点ICP1来衡量,图9所示为输入1 dB压缩点的仿真结果,ICP1功率为0.065 mW。该线性度并不是本文能实现的最佳线性度性能。为了兼顾低噪声系数必须降低一定程度的线性度,但是与传统结构相比,本文实现的线性度性能已得到很大提高。各性能参数的比较如表1所示。

从表1可以看出:本文设计的BiFET LNA贡献极低的噪声系数0.9 dB,同时提供19 dB的功率增益和较好的线性度,且只消耗3.7 mA电流。综合考虑各项指标参数,本文设计的BiFET LNA与其他文献相比具有很大的优势。

表1 本文的LNA性能与文献中的性能对比

Table 1 Performance comparison with references

4 结论

(1) 设计了一种用于GPS卫星导航系统的低噪声、高增益、高线性度射频低噪声放大器。电路采用BiFET Cascode结构以便于噪声、增益和线性度之间的折中设计。通过对作为输入管的HBT管进行尺寸和偏置电流密度等的优化设计,使得其噪声性能达到最优,经过优化后该管的偏置电流密度为0.1 mA/μm2,能提供最小0.453 dB的噪声系数;Cascode管采用MOSFET管以提供优良的线性度,其长×宽为120 μm×0.18 μm。

(2) 该BiFET LNA在华虹HHNEC 0.18 μm SiGe BiCMOS工艺上实现,在2.85 V电源电压下工作,消耗3.7 mA电流。版图后仿真结果表明,该BiFET LNA能提供19 dB的功率增益,0.9 dB的超低噪声系数,输入1 dB压缩点ICP1为0.065 mW。

参考文献:

[1] Liang Q Q, Niu G F, Cresslel J D, et al. Geometry and bias current optimization for SiGe HBT cascode low-noise amplifiers[C]// IEEE Radio Frequency Integrated Circuits Symposium. Seattle: Microwave, 2002: 407-410.

[2] Lin C H, Su Y K, Juang Y Z, et al. The effect of geometry on the noise characterization of SiGe HBTs and optimized device sizes for the design of low-noise amplifiers[J]. IEEE Transactions on Microwave Theory and Techniques, 2004, 52(9): 2153-2162.

[3] DUAN Lian, HUANG Wei, MA Chenyan, et al. A single-to- differential low-noise amplifier with low differential output imbalance[J]. Chinese Journal of Semiconductors, 2012, 33(3): 0350021-0350025.

[4] HAN Wentao, QI Yu, YE Song, et al. Radio frequency low noise amplifier with linearizing bias circuit[J]. Journal of Electronic Science and Technology of China, 2009, 7(2): 160-164.

[5] Poh J C H, Cheng P, Thrivikraman T K, et al. High gain high linearity L-band SiGe LNA with fully-integrated matching network[C]// Proceedings of the 10th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems. New Orleans, 2010: 69-72.

[6] Yang Y C, Lee P W, Chiu H W, et al. Reconfigurable SiGe low-noise amplifiers with variable miller capacitance[J]. IEEE Transactions on Circuits and Systems, 2006, 53(12): 2567-2577.

[7] Kuo W M L, Liang Q Q, Cressler J D, et al. An X-band SiGe LNA with 1.36 dB mean moise figure for monolithic phased array transmit/receive radar modules[C]// IEEE Radio Frequency Integrated Circuits Symposium. San Francisco, 2006: 498-501.

[8] Min B W, Rebeiz G M. Ka-band SiGe HBT low noise amplifier design for simultaneous noise and input power matching[J]. IEEE Microwave and Wireless Components Letters, 2007, 17(2): 891-893.

[9] Voinigescu S, Maliepaard M, Showell J, et al. A scalable high-frequency noise model for bipolar transistors with application to optimal transistor sizing for low-noise amplifier design[J]. IEEE J Solid State Circuits, 1997, 32(9): 1430-1439.

[10] Sun K, Tsai Z, Lin K, et al. A noise optimization formu-lation for CMOS low-noise ampli fiers with on-chip low-Q inductors[J]. IEEE Transactions on Microwave Theory and Techniques, 2006, 54(4): 1554-1560.

[11] Ma P X, Marco R, Zheng J, et al. A novel bipolar-MOSFET low-noise amplifier (BiFET LNA), circuit configuration, design methodology, and chip implementation[J]. IEEE Transactions on Microwave Theory and Techniques, 2003, 51(11): 2175-2180.

[12] Moreira C P, Kerherve E, Jarry P, et al. A low-consumption LNA using a 0.25 μm 60 GHz fT SiGe:C BiCMOS7RF technology for wireless applications[C]// Proceedings of the IEEE Mediterranean Microwave Symposium. Hsinchum, 2004: 584-1587.

[13] Sivonen P, Kangasmaa S,  A. Analysis of packaging effects and optimization in inductively degenerated common-emitter low-noise amplifiers[J]. IEEE Transactions on Microwave Theory and Techniques, 2003, 51(4): 1220-1226.

A. Analysis of packaging effects and optimization in inductively degenerated common-emitter low-noise amplifiers[J]. IEEE Transactions on Microwave Theory and Techniques, 2003, 51(4): 1220-1226.

[14] HOU Xunping, ZHAO Yuanfu, LI Weimin, et al. Design of SiGe BiCMOS LNA with ESD protection for multi-band navigation receiver front-end[C]// 5th International Conference on MEMS NANO, and Smart Systems. Dubai, 2009: 93-96.

[15] Park Y, Lee C H, Cressler J D, et al. The analysis of UWB SiGe HBT LNA for its noise, linearity, and minimum group delay variation[J]. IEEE Transactions on Microwave Theory and Techniques, 2006, 54(4): 1687-1697.

[16] LI Hui, MA Zhenqiang, NIU Guofu. Transport shot noise models and NFmin comparison for SiGe HBTs under different operation configurations[C]// Proceedings of the 2nd European Microwave Integrated Circuits Conference. Munich, 2007: 203-206.

[17] ZHANG S M, Guofu N, Cressler J D, et al. The effects of geometrical scaling on the frequency response and noise performance of SiGe HBTs[J]. IEEE Transactions on Electron Devices, 2002, 49(3): 429-435.

[18] Patel V J, Axtell H S, Cerny C L, et al. X-Band low noise amplifier using SiGe BiCMOS technology[C]// Proceedings of the IEEE CSIC International Conference. Singapore, 2005: 49-52.

[19] Pourakbar M, Langari P, Dousti M, et al. A 1.2-V Single-stage, SiGe BiCMOS low-noise amplifier at 5.8 GHz for wireless applications[C]// Proceedings of the 3rd ICTTA International Conference. Damascus, 2008: 1-5.

(编辑 赵俊)

收稿日期:2012-10-15;修回日期:2013-01-10

基金项目:嘉兴市科技计划项目(2012BZ5006);嘉兴市南湖区科技计划项目(2011QG06);国家“核高基”重大专项(2009ZX01031-002-008)

通信作者:马成炎(1963-),男,江苏南通人,研究员,博士生导师,从事模拟射频集成电路和无线通信系统的设计和研究;电话:13670009918;E-mail: machengyan@casic.ac.cn