���±��: 1004-0609(2005)05-0746-05

(Cr-Si-Ni)/Si��Ĥ���۽ṹ�͵�����

������, ����ƽ, �⽨��

(�Ϻ���ͨ��ѧ ���Ͽ�ѧ�빤��ѧԺ ���������²��ϼ������ص�ʵ����, �Ϻ� 200030)

ժ Ҫ: ���ôſؽ��䷽����Si(100)�������Ʊ���Cr-Si-Ni���象Ĥ, �о��˲�ͬ�¶��˻�ʱ��Ĥ�۽ṹ��ת������Լ��Ե����ʵ�Ӱ�졣 �������: ��Ĥ�ڽ���̬�͵���300���ȴ���ʱΪ�Ǿ�̬; �˻��¶ȸ���300���Ժ�, ��Ĥ������CrSi2������; ���˻��¶ȴﵽ600��ʱ, ��Ĥ�л��������ྦྷSi������, ͬʱ�ڱ�Ĥ������洦��������ԭ�ӵ����ɢ; CrSi2������ɡ�����״�ṹ, ��ɢ�ֲ��ڷǾ���Ե������; ��Ĥ���µ����������˻��¶ȵ�����, ���������� ���½�����; ��Ĥ���������˻��¶ȵı仯��Ϊ�뱡Ĥ�۽ṹ�ı仯�Լ�������ɢ�йء�

�ؼ���: ���象Ĥ; Si����; �۽ṹ; ������ɢ; ������ ��ͼ�����: TM241.1

���ױ�ʶ��: A

Microstructure and electrical resistivity of Cr-Si-Ni films deposited on Si substrates

ZHANG Yu-qin, DONG Xian-ping, WU Jian-sheng

(Key Laboratory for High Temperature Materials and Tests of Ministry of Education,

School of Materials Science and Engineering, Shanghai Jiaotong University,

Shanghai 200030, China)

Abstract: Cr-Si-Ni resistive films were prepared on n-type Si (100) substrates by magnetron sputtering. The microstructure evolution and electrical resistivity of the films as a function of annealing temperatures were investigated. The results reveal that the microstructure of the films at as-deposited state and annealed at temperature lower than 300�� are amorphous state. With the annealing temperature increases to higher than 300��, the nanocrystalline CrSi2 begins to appear. A few polycrystalline Si phase is separated at the films, and an atomic interdiffusion at the interface between the films and Si substrates can be observed, when the annealing temperature reaches 600��. Cr-Si-Ni films consist of the nanocrystalline phase as an island dispersed in amorphous insulating matrix. With the annealing temperatures increasing, the room temperature resistivity of the films rises at the beginning, then goes down. The annealing behavior of the resistivity is correlated with the microstructure and interfacial diffusion of the films.

Key words: resistive film; Si substrates; microstructure; interfacial diffusion; electrical resistivity

Cr-Siϵ�軯�ﱡĤ���ھ��нϸߵ�Ƭ������ʡ� ��С�ĵ����¶�ϵ��(TCR)�Լ����õ����ȶ��Ժͻ�ѧ�ȶ���, ��Ϊ���ɵ�·�������豸�зdz����������ĵ��象Ĥ����[1-4]�� ����Ϊֹ, ʹ���ڼ��ɵ�·�еĹ軯����象Ĥ�����ý���������Si�����Ͼ���ɢ��Ӧ�����γ�, ��������������[5-8]�� ���Dz�����ɢ���Ʊ��ĵ���Ԫ�����˴��ڽ���ƽ���Ȳ ������������ ���ȶ��Բ �ظ������Բ��á� ��ķ����Ե�ȱ����, ����Ҫ��ȱ���Ǻ��ѻ�øߵĵ���ֵ�� ����һЩ��Ҫ�ϸ���ֵ��ĤԪ���ĵ����豸, �������������� ��Яʽ�����豸��, ��ɢ���Ʊ���Ԫ���ͺ��������Ҫ�� �����Щȱ��, ����ͨ���ڻ�����Ԥ���Ʊ���Ե�м��, Ȼ���ٽ���Ĥ�������м���ϵķ������˷�������[9, 10]�� Ȼ���м��ļ��벻���ᵼ�³ɱ�������, �������ڱ�Ĥ�������Ի��dz�����, �����м�㱾���ֻ�����µ�ȱ��, �Ӷ������µ����⡣ ���, �о����軯�ﱡĤֱ�ӳ����ڹ������, ��Ϊ���象ĤӦ���ڼ��ɵ�·�������豸������Խ��Խ�����Ȥ��

������, ������ɢ���Ʊ��軯����象Ĥ���о��϶�[5-8], �����ý�Cr-Siϵ�軯�ﱡĤֱ�ӳ�����Si������, ���о����۽ṹ�͵����ܵ����ױȽ��١� ����ǰ���о����, ��Cr-Si�Ͻ�в��м���3%~6%Ni(Ħ������)���Ը��Ʊ�Ĥ�ĵ����ܺͰвĵ��Ʊ��ӹ�����[11, 12]�� �������߲���Cr17Si80Ni3�Ͻ�в�ͨ����Ƶ�ſؽ��䷽����n��Si(100)�������Ʊ���Cr-Si-Ni��Ĥ, �о����ȴ��������б�Ĥ�۽ṹ��ת����̺ͽ�����ɢ���, �������۽ṹ��������ɢ�Ա�Ĥ�����ʵ�Ӱ�졣

1 ʵ��

��������������Ʊ���Cr-Si-Ni�Ͻ�в�, �ɷ�ΪCr17Si80Ni3, Ȼ��ʹ��CEVP-1000C����Ƶ�ſؽ������Ʊ���Ĥ�� ��Ĥ�����ڵ�����n��Si(100)������, ����ǰ������Ԥ������ �����ұ�����ն�Ϊ1��10-4Pa, ����������, ����ͨ�����, ʹѹ��ʼ�ձ�����0.4Pa, ���书�ʹ̶���300W, ��Ĥ��ȿ�����300nm��1��m, ��Ƭ�ڳ��������д�������״̬�� �Ʊ��ı�Ĥ����ʽ����¯�����ȴ���, ����ձ���, �˻��¶ȷ�Χ250~600��, ���50���ȴ���, ����180min��

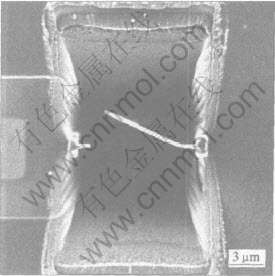

��Ĥ�����ALPHA-STEP 500���������Dz���, ���Ϊ1��m�ı�Ĥ���������dzɷַ���, �������Զ��ں��300nm�ı�Ĥ�Ͻ��С� �۽ṹ�����ֱ���DMAX-111��X����������(XRD)��Hitachi H800 ����羵(TEM)�Ͻ���, �ɷ���ȷ�������PHI 550 ESCA/SAM ��Ъ������(AES)����, ������̽�������(SDY-5��)������ͬ�¶ȴ�����Ĥ�����µ����ʡ� �ݶ��� TEM ����ͨ��SEIKO FIB-SMI2200�۽�������ϵͳ(FIB)���Ʊ�(ͼ1), ����岽�������[13]�� �Ʊ����������ߴ�Ϊ10��m ��5��m��160nm�� ����AES����ʱ, һ�ε�������ѹ3keV, ����1��A, Ar+���ӿ�ʴ�����ܶ�100��A/cm2, ��ѹ3kV, ��ʴ�����ٶ�ԼΪ12nm/min��

ͼ1 �۽�������ϵͳ�Ʊ���Cr-Si-Ni��Ĥ�ݶ���TEM��

Fig.1 Cross-sectional TEM image of Cr-Si-Ni films prepared by

using focused ion beam system (FIB)

2 ����������

2.1 ��Ĥ�۽ṹ����

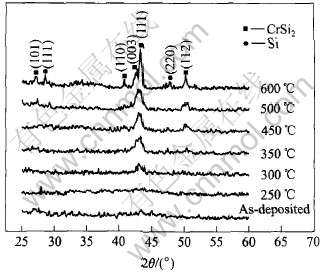

�������Ž���, ���䱡Ĥ�Ļ�ѧ�ɷ���вĵĻ�ѧ�ɷִ���һ����ƫ��, ��EDX������, Cr-Si-Ni���䱡Ĥ��ƽ����ѧ�ɷ�(Ħ������)Ϊ: Cr 21.66%, Si 74.47%��Ni 3.88%�� ͼ2 ��ʾΪ����̬�Ͳ�ͬ�¶��˻���180min��Si����Cr-Si-Ni ��Ĥ��X����������(���������̫��, ���������25�����º�60�����ϵ�����ͼ���Ժ���)�� ��ͼ�п������Կ���, ��Ĥ�ڽ���̬������300���ȴ���ʱ�ʷǾ�̬; �ȴ����¶ȸ���300���Ժ�, ͼ���г�����CrSi2(111)�����������, ˵����Ĥ����CrSi2����������; �����ȴ����¶ȵĽ�һ������, CrSi2�������ǿ������; ��450��ʱͬʱ������CrSi2(112)�����; ���ҵ��˻��¶ȴﵽ600��ʱ, ͼ���в��������˸��ྦྷ���CrSi2�������, ���ҷ����жྦྷSi���������֡� ͨ����600�洦���ĵ���Si����XRD��������, ֤���ڱ�Ĥ��ȷʵ�жྦྷSi�������� ����, ����ͼ2�����Կ��������ȴ����¶ȵ�����, CrSi2�����ijߴ������� ���ڱ�Ĥ��Ni��������, X��������û�м���Ni�����(��NiSi��NiSi2��)�����ߡ�

ͼ2 ����̬�Ͳ�ͬ�¶����˻���180min��Cr-Si-Ni��Ĥ��X����������

Fig.2 XRD patterns of Cr-Si-Ni films at as-deposited state and annealed at different temperatures for 180min

ͼ3��ʾΪ��Ĥ��500���600���ȴ���180min����ݶ���TEM��ò��ѡ����������(SAED)�� ��ͼ�п��Կ���, ��Ĥ���д���CrSi2����������, ����XRD���õĽ����һ�µġ� CrSi2������ɡ�����״�ṹ, ��ɢ�ֲ��ڷǾ���Ե�����ϡ� ���˻��¶�Ϊ600��ʱ, ���Թ۲쵽����ľ���������, ���Ҿ��������ٶȿ�, �ܶྦྷ����ʼ�ž���һ��, ����������Ա�500��ʱ�½��ܶ�, ��Ա�Ĥ�ĵ����ʽ������ܴ��Ӱ�졣 ͬʱ����ͼ3�����Կ���, ��Ĥ����Ľ���ƽ��, ˵���ȴ��������б�Ĥ���洦û����������ɢ��

ͼ3 (Cr-Si-Ni)/Si��Ĥ��500��(a)��600��(b)�ȴ���180min���ݶ����TEM��ò��ѡ���������仨��

Fig.3 Cross-sectional TEM micrographs and SAED patterns of Cr-Si-Ni films deposited on Si substrates annealed at 500��(a) and

600��(b) for 180min

2.2 ��Ĥ��AES��ȷ���

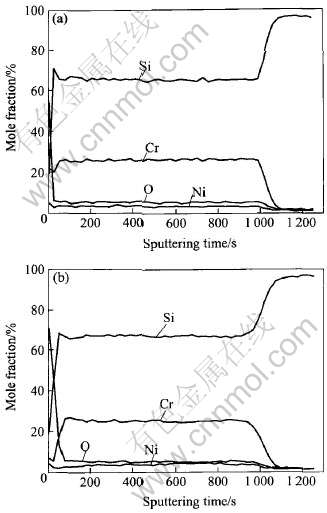

ͼ4��ʾΪ������Si�����ϵ�Cr-Si-Ni��Ĥ����̬��600���ȴ���180min���AES��ȷֲ����ߡ� ͼ4(a)��ʾΪ�ڽ���̬������Si�� Cr�� Ni��OԪ�ص����ԭ�Ӻ����� ��ͼ�п��Կ���, �ڱ�Ĥ����, Si�� Cr�� NiԪ�صķֲ��ȽϾ��ȡ� �����ڱ�Ĥ����Ľ��紦, Si�� Cr�� NiԪ�صķֲ��뱡Ĥ����ڲ���, Cr��NiԪ�صĺ���Ҫ���ڱ�Ĥ��, Si����Ҫ�Ը��ڱ�Ĥ��, ��ԭ����Ҫ������Si���ױ���ֲڶ�����ġ� ͼ4(b)��ʾΪSi����Cr-Si-Ni��Ĥ��600���ȴ���180min��AES��ȵķֲ��� ���Կ���, �ȴ����Ժ�ı�Ĥ��������Ŀ��ȱȽ���̬������������������, ������ڱ�Ĥ��Si���Ľ����Ϸ�����Ԫ�ص����ɢ�� �ڽ��洦������Cr��Si������ɢ��Si�ĸ���, ������Si���Զྦྷ����ʽ������ ���˵����ͼ2��, ��Ĥ��600���ȴ�������ֶྦྷSi���ԭ�� ��ͼ4�����Կ���, ��������Ŀ��Ƚ�С, ˵��������ɢ�̶Ȳ��Ǻܴ�, ����ͼ3(b) ����õ�TEM�����Ǻϡ� ��������Ʊ���Cr-Si-Ni��Ĥ��Si�����Ͼ��нϺõ����ȶ��ԡ�

2.3 �۽ṹ�ͽ�����ɢ�Ա�Ĥ�����ܵ�Ӱ��

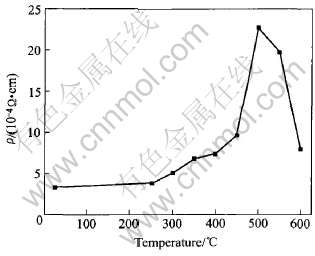

ͼ5��ʾΪSi����Cr-Si-Ni��Ĥ�ڽ���̬�Ͳ�ͬ�¶��˻���180min������µ����ʡ� ��ͼ�п��Կ���, ��Ĥ���µ����������˻��¶ȵ�����, ���������� ���½����ơ� ���˻��¶ȵ���300��ʱ, ��Ĥ�����������¶ȵ���������������; ���˻��¶ȸ���300���Ժ�, ��Ĥ�����ʵ������ٶȼӿ�; �ر����˻��¶�500��ʱ, ��Ĥ�����ʷ���Ծ��, �ﵽ���ֵ; ���������¶ȵĽ�һ������, �����ʷ��������½��� ��Ĥ���������˻��¶ȵı仯��Ϊ�뱡Ĥ�ȴ����������۽ṹ�ı仯�Լ�������ɢ�зdz���Ĺ�ϵ, ��Ӱ�����������Neugebauer��Webb������IJ�����������Ĥ�Ļ��������[14]�����͡� ��������۵ı����ǰ������ӵ��Ȼ��������������ЧӦ���������� ��������Ϊ�����Ȼ�Ľ��, ���Ӵ�һ������С��������һ������С��, �Ӷ�ʹԭ�����Ե�һЩС�������˵�ɡ� �ڴ���С��������С����ĵ��Ӵ�������һ���������̡�

ͼ4 (Cr-Si-Ni)/Si��Ĥ����̬��600���˻���180min��AES��ȵķֲ�

Fig.4 Auger depth profiles of Cr-Si-Ni films

deposited on Si substrates at as-deposited

state(a) and annealed at 600�� for 180min(b)

ͼ5 (Cr-Si-Ni)/Si��Ĥ�ڽ���̬�Ͳ�ͬ�¶����˻���180min������µ�����

Fig.5 Room temperature resistivity of Cr-Si-Ni films deposited on Si substrates at

as-deposited state and annealed at various temperatures for 180min

���ݻ��������, ��һ���¶��µı�Ĥ����R���Խ��Ʊ�ʾΪ[9, 15]

ʽ�� C��AΪ����; kΪ������������; rΪС���뾶; sΪ�������; qΪ���ӵ����; ��Ϊ��Ч��Ե����; ��ΪС��֮����Ч���ݸ߶�, �뵺�ı���λ���йء� �ڱ�Ĥ��Ⱥͱ����ȷ���������, ʽ(1)��ӳ�˱�Ĥ��������С���ߴ�͵������֮��Ĺ�ϵ��

����ʽ(1)��(2), ��Ĥ���������ŵ��뾶���������С�� ���ŵ��������������, ���ǵ����Ե����ʵ�Ӱ��Ҫ�ȵ��뾶��Ӱ���ö�, ��˱�Ĥ�����ʵı仯����������ڵ����ı仯�� ����ǰ��ķ���, �����α�Ĥ�ɺܶ������С�����, ���ڻ����ڳ���������һֱ���ֵ���״̬, �����ЩС��������ԭʼλ��; ���ų����IJ��Ͻ���, ����Ľ������ӳ����ڻ�����, �Ӷ��γ���һ����������ı�Ĥ�� ���˻��¶ȵ���300��ʱ, ��Ĥ�ʷǾ�̬�ṹ�� �������µ�����, ��Ĥ�е�С�������ƶ�, �γ�����ɢ��С��Ⱥ, ���ҳߴ�ͼ��Ҳ�ڻ�������, �����Ĥ�����ʻ�����ߡ� �˻��¶���300~500��֮��ʱ, ����õ���������, ��Ĥ��������������CrSi2����, �����侧����С�ͼ��Ҳ��������, CrSi2�������ž۳ɽϴ��С��Ⱥ��ɢ�ֲ��ڷǾ���Ե�����ϡ� ���������¶ȷ�Χ��, �������Ⱦ�����С������Ҫ��һЩ, ��Ĥ��������֮Ѹ������ ���¶ȳ���500���Ժ�, ������CrSi2��������������ͳߴ缱������, ���¾������Ѹ�ټ�С(ͼ3), ����ʹ�ñ�Ĥ�����ʷ��������½���

����Si����Cr-Si-Ni��Ĥ, ����������˻��¶ȵı仯��Ϊ��Ҫ���۽ṹ�йء� �����ڽϸ��¶��˻�ʱ��Ĥ����Ľ�����ɢ�Ե�����Ҳ��һ����Ӱ�졣 ��ͼ4��֪, �����˻��¶ȵ�����, �ڱ�Ĥ��Si�������Ϸ�����ԭ�ӵ����ɢ, �γ���һ����С�Ľ�����ɢ�㡣 �������������ɢ��Ŀ��ȷdz���С, Ȼ�����ڵ���������뱡Ĥ����ܻ��γɡ���������·, ���˵���ġ�����������, �Ӷ��ᵼ�±�Ĥ�ĵ�������һ���ļ�С�� ���ڱ���ʵ�����Ʊ��ı�Ĥ, ������ɢ��Ŀ��ȷdz�С, ����Ե����ʵ�û��������Ӱ�졣 ���, �����Ϸ������Կ���, ��Cr-Si-Ni��Ĥֱ�ӳ����ڵ���Si�����Ͽ����ڽϵ͵��ȴ����¶��»�ýϸߵĵ�����, ���Կ˷���ɢ���Ʊ���Ĥ���������һЩ���⡣

3 ����

���ôſؽ��䷨�Ʊ���Si(100)�����ϵ�Cr-Si-Ni���象Ĥ�ڽ���̬������300���ȴ���ʱ�ʷǾ�̬�ṹ; �˻��¶ȸ���300���Ժ�, ��Ĥ������CrSi2������; ���˻��¶ȴﵽ600��ʱ, ��Ĥ���������ྦྷSi�������� CrSi2������ɡ�����״�ṹ, ��ɢ�ֲ��ڷǾ���Ե�����ϡ� �����ȴ����¶ȵ�����, ��Ĥ�о�����ߴ粻������ �ڸ����˻�ʱ, ��Ĥ��Si���Ľ��洦������ԭ�ӵ����ɢ, ��������ɢ��Ŀ��ȷdz�С, ˵����Ĥ���нϺõ����ȶ��ԡ� ��Ĥ���µ����������˻��¶ȵ�����, ���������� ���½����ơ� ��Ĥ���������˻��¶ȵı仯��Ϊ�뱡Ĥ�ȴ����������۽ṹ�ı仯�Լ�������ɢ�йء�

REFERENCES

[1]Br��ckner W, Grie�xmann H, Schreiber H, et al. Degradation of CrSi(W)-O resistive films[J]. Thin Solid Films, 1992, 214: 84-91.

[2]Br��ckner W, Grie�xmann H, Monch J I, et al. High temperature stability of CrSi(W)-N films[J]. Thin Solid Films, 1992, 221: 140-146.

[3]ZHANG Yu-qin, DONG Xian-ping, WU Jian-sheng. Microstructure and electrical characteristics of Cr-Si-Ni films deposited on glass and Si(100) substrates by RF magnetron sputtering[J]. Materials Science and Engineering B, 2004, 113: 154-160.

[4]����ƽ, �⽨��, ë����. ��Ԫ�ض�Cr-Si-Al���象Ĥ������Ϊ�������ܵ�Ӱ��[J]. �й���ɫ����ѧ��, 2002, 12(4): 668-672.

DONG Xian-ping, WU Jian-sheng, MAO Li-zhong. Effect of nitrogen on crystallization behavior and electrical properties of Cr-Si-Al resistive films[J]. The Chinese Journal of Nonferrous Metals, 2002, 12(4): 668-672.

[5]Mirouh K, Bouabellou A, Halimi R, et al. Microstructural study of annealed Cr/Si system using cross-sectional TEM combined with nano-analysis[J]. Materials Science and Engineering B, 2003, 102: 80-83.

[6]Mirouh K, Bouabellou A, Halimi R, et al. Cross-sectional TEM investigations of the influence of P+ ions implanted in the Si substrate on the atomic interdiffusion in the Cr-Si system[J]. Materials Science and Engineering B, 2000, 73: 116-119.

[7]Labbani R, Halimi R, Bouabellou A, et al. Elaboration of thin chromium silicide layers on P+ implanted silicon[J]. Nuclear Instruments and Methods in Physics Research A, 2002, 480: 223-228.

[8]Zhu H N, Liu B X. Pattern evolution during the growth of CrSi layers on Si (111) upon high current pulsed Cr ion implantation[J]. Thin Solid Films, 2001, 384: 53-57.

[9]Wu F, McLaurin A W, Henson K E, et al. The effect of the process on the electrical and microstructure characteristics of the CrSi thin resistor films: part��[J]. Thin Solid Films, 1998, 332: 418-422.

[10]Gong S F, Li X H, Hentzell H T G. Electrical and structural properties of thin films of sputtered CrSi2[J]. Thin Solid Films, 1992, 208: 91-95.

[11]����ƽ. ��ԪCr-Siϵ�軯�ﱡĤ�۽ṹ�͵����ܵ��о�[D]. �Ϻ�: �Ϻ���ͨ��ѧ, 2003.

DONG Xian-ping. The Study of Microstructure and Electrical Properties of Cr-Si Silicide Films[D]. Shanghai: Shanghai Jiaotong University, 2003.

[12]Dong X P, Wu J S. Study on the crystallization of amorphous Cr-Si-Ni thin films using in situ X-ray diffraction[J]. Journal of Materials Science and Technology, 2001, 17: s43-46.

[13]Longford R M, Clinton C. In situ lift-out using FIB-SEM system[J]. Micron, 2004, 35: 607-611.

[14]Neugebauer C A, Webb M B. Electrical conduction mechanism in ultrathin evaporated metal films[J]. Journal of Applied Physics, 1962, 33(1): 74-80.

[15]Wu F, Morris J E. The effects of hydrogen absorption on the electrical conduction in discontinuous palladium films[J]. Thin Solid Films, 1994, 246: 17-23.

������Ŀ: ������Ȼ��ѧ�����ص�������Ŀ(50131030); �Ϻ��пƼ���չ����������Ŀ(02DJ14042)

�ո�����: 2004-11-22; ������: 2005-03-21

�����: ������(1976-), ��, ��ʿ�о���.

ͨѶ����: ������, ��ʿ�о���; �绰: 021-62932440; E-mail: zyqkust@sjtu.edu.cn

(�༭������)